# A40i硬件设计指南

# CONTENTS

01 24M晶振

05 NAND

02 AUDIO CODEC

06 ETHERNET

03 CSI

07 HDMI

04 EMMC

08 RGB/LVDS/DSI

# CONTENTS

09 SATA

13 TVOUT/CVBS/VGA

10 SDIO

14 USB

11 TS

15 WIFI/BT

12 TVIN

16 GPS

# CONTENTS

17 THERMAL

21 KEY

18 ESD

22 STACK UP

19 PMU

23 SOC FANOUT

20 DRAM

24 REVISION HISTORY

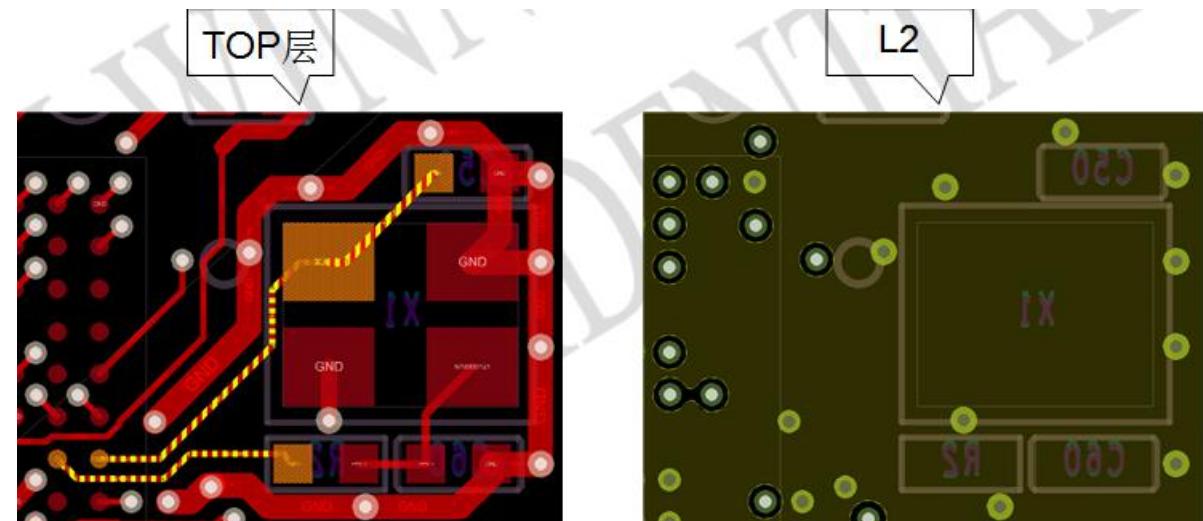

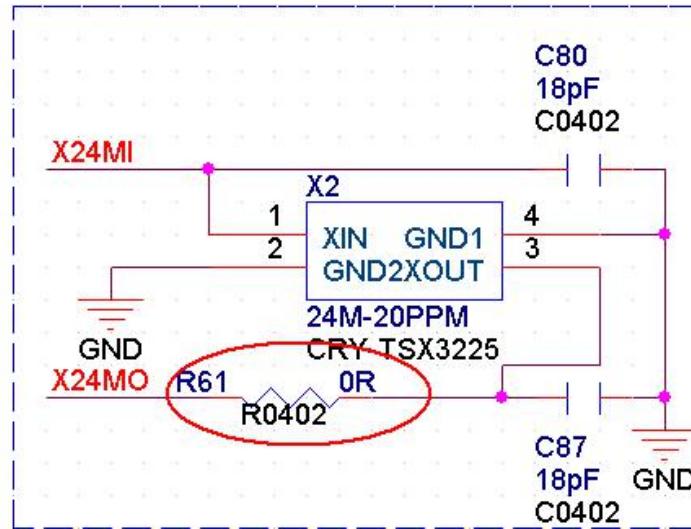

# 01 24M晶振

1. 高频晶振的网络X24MO上串接电阻必须保留，方便调试时钟信号幅度，晶振选型20 ppm/无源晶振。

2. 晶体尽量靠近IC摆放，避免晶体走线过长。

3. 晶振的匹配电容必须靠近晶振摆放

4. 晶体及其走线区域的外围和相邻层，用GND屏蔽保护。

5. 晶体及其走线区域的相邻层，禁止其它走线。

## 02 AUDIO CODEC

1. AVCC、VRP、VRA1、VRA2和AGND接地电容、电阻依次靠近主控摆放。

2. AVCC走线 $\geq 25$  mil；VRP、VRA1、VRA2线宽 $\geq 10$  mil；线长 $\leq 300$  mil。远离高速干扰信号。

3. AGND需有一片覆铜。覆铜宽度 $\geq 80$  mil，AGND接地电阻连接到GND平面的过孔 $\geq 2$ 个。

4. AVCC VRA1 VRA2 VRP、HPCOMFB接地电容、电阻连接到AGND覆铜。

5. VCC-HP、HPBP电容靠近芯片放置。走线需大于10mil。

6. GND-HP从芯片出来直接连接GND。

7. HPOUTL、HPCOM、HPCOMFB、HPOUTR并行走线并包地，HPOUTL、HPOUTR在两旁，HPCOM、HPCOMFB在中间，整组包地。线宽10 mil。走线及过孔远离高速信号及时钟信号。

## 02 AUDIO CODEC

8. MIC 摆放位置靠近电路板的边沿，远离 ( $>=200\text{mil}$ ) RF、PA、开关电源。

9. ESD 器件必须靠近MIC摆放，从MIC引出来的走线必须先经过ESD器件，在连接其他器件。

10. MICxP、MICxN，类差分走线，线宽4mil，线距4mil，包地。

11. LINEINL、LINEINR、FIMINL、FMINR每对L、R信号分别包地，线宽4mil。走线及过孔远离高速信号及时钟信号。

12. PHONEOUTP、PHONEOUTN、HPOUTL、HPOUTR每对P、N信号分别类差分走线，线宽4mil，线距4mil，包地。

13. 当外部使用功放IC时,外部功放仿真板子的PCB板的边沿,电源走线宽度 $>=15\text{mil}$ , 输入输出信号线线宽10mil，并包地。

## 02 AUDIO CODEC

- 14.耳机接法必须考虑实际采用的耳机座子与信号的连接关系，并考虑采用欧标或者美标四段式耳机。

- 15.HPOUTL HPOUTR如果做耦合的方式输出需要把HPCOMFB HPCOM这两个脚拉一个对地1uF电容。

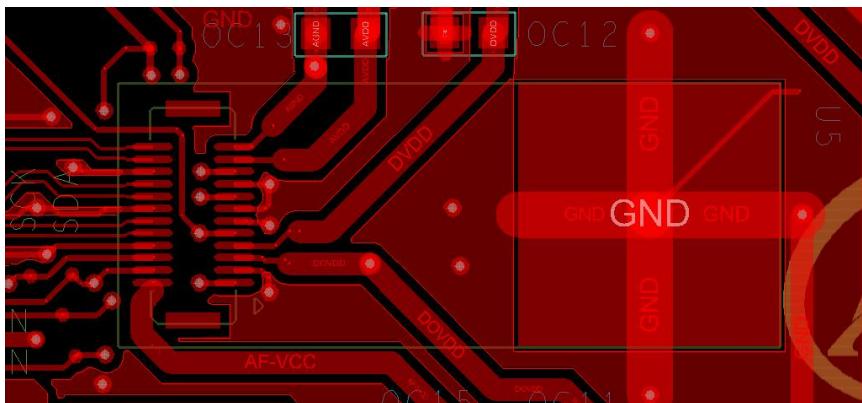

# 03 CSI

1. CSI模组走线线宽15~20mil

2. 为保证Sensor 模组接地良好，模组散热焊盘尽可能通过多个点与大片GND连接。

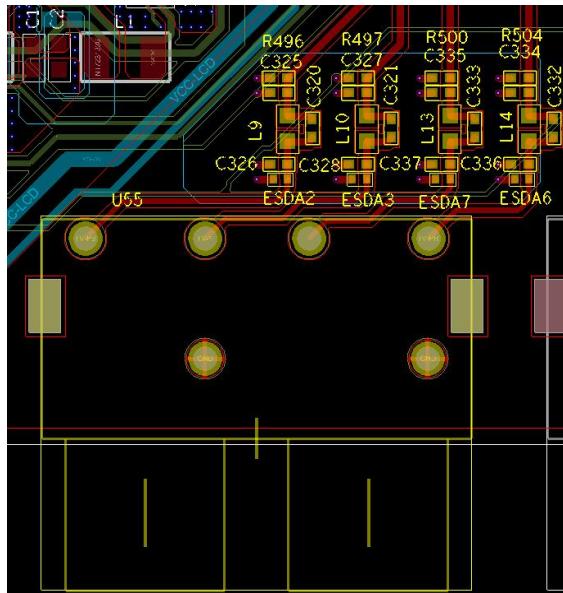

3. PCB对应模组位置需紧贴大面积的金属，以便散热。如下图所示：

4. PCLK的对地电容靠近主控，串联电阻靠近模组；

5. MCLK的对地电容靠近模组，串联电阻靠近主控；

## 03 CSI

6. Hsync的对地电容靠近主控；

7. Vsync、Hsync、Data串联电阻靠近模组；

8. 为了避免模组端的电容、电阻、排阻等器件被其他元器件遮挡，影响调试，建议统一放置在背面；

9. 保证模具的摄像头开孔位置，与摄像头插座位置的距离尽量近，防止摄像头模组FPC过长出现问题；

10. 电源滤波电容靠近模组放置；

11. MCLK和PCLK需要各自包地，如下图所示；如果PCB空间有限，不能保证信号线完整包地时，需保持该信号线在间距 $\geq 15\text{mil}$ 空间内无其他走线；

## 03 CSI

12. 连线时保证较少的换层 ( MCLK、PCLK换层过孔≤2个 )。

13. PCLK和Data走线长度尽量一致，允许相差不超过500mil，尽量不要因为追求等长而走蛇形线等等。

14. 走线间距大于2倍线宽。

15. PCLK和MCLK上必须增加NC电容或者OR电阻用于提高摄像头的兼容性以及降低时钟信号的EMI辐射。

16. AVDD-CSI与IOVDD-CSI必须单独供电，以保证AVCC-CSI的稳定性。

17. 若模组带自动对焦功能，由于给内部VCM的供电的AF-VCC电源噪声较大，注意不要与其他敏感电源 ( 如AVDD ) 共用。

## 03 CSI

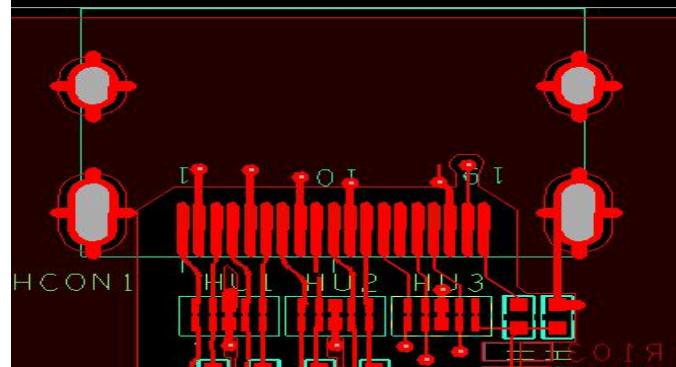

18. 摄像头模组PIN脚定义：检查摄像头模组的PIN定义，是否与插座一致。特别需要注意一般24PIN插座有上接触或下接触可选择，检查模组金手指接触面的方向。

19. 如果前后摄像头上电时序完全不同时，必须分开AVDD和IOVDD

# 04 EMMC

1. DS信号在HS400模式下是读操作的时钟信号，因此走线的要求与CLK信号基本相同。

2. eMMC靠近主控摆放。如果主控对应GPIO使用独立电源供电（通常为VCC-PC），则将去耦电容靠近主控端供电输入引脚摆放

3. VCCQ, VCC, VDDi的所有去耦电容均靠近eMMC摆放。

4. CLK信号串接电阻靠近主控摆放，串阻与主控CLK连接走线距离≤300mil。

# 04 EMMC

## 5. 信号线走线要求：

- ( 1 ) eMMC与主控间走线长度 $\leq$ 2000mil ；

- ( 2 ) 走线阻抗50欧；

- ( 3 ) 线间距 $\geq$ 2倍线宽；

- ( 4 ) D0~D7、DS相对CLK等长控制 $\leq$ 300mil ；

- ( 5 ) D0~D7上使用过孔的数量尽量相同。

## 6. 除Reset外，务必保证所有信号走线参考平面完整，示意图如下：

## 04 EMMC

7. VCC,VCCQ线宽不小于12mil，或直接使用敷铜代替电源走线。电源线上如有过孔，则过孔数量不少于2个，避免过孔限流影响供电。

8. CLK和DS信号做包地处理，包地通过过孔与GND平面连接。如果不能包地则保持线间距 $\geq$ 3倍线宽。

9. 走线尽量避开高频信号。

10. eMMC NC/RFU等保留引脚都悬空，不可为了走线方便将这些信号与电源、地、或其他eMMC信号连接在一起。如果确实走线有困难，可适当修改eMMC PCB封装，去掉一些NC/RFU的ball。

11. 如果期望eMMC运行在较高频率，则建议只使用eMMC，保证主控IO与eMMC点对点连接。如果NAND/eMMC双Layout时，走线采用菊花链方式，将eMMC作为走线的终点，尽量减少分叉线长度(标案中U52和U50 双layout叠放，放置于菊花链最末端，U51放置于SOC和EMMC的中间位置)

# 05 NAND

1. RE、WE、DQS本质上是一个时钟信号线，用于数据采样

2. NAND应靠近主控摆放。

3. 如果主控对应GPIO使用独立电源供电（通常为VCC-PC），则将去耦电容靠近主控端供电输入引脚摆放。

4. VCCQ, VCC的所有去耦电容均靠近NAND摆放。

5. RE、WE、DQS信号串接电阻靠近主控摆放，串阻与主控连接走线距离≤300mil。

# 05 NAND

6. NAND与主控走线间走线 $\leq$ 2000mil，信号走线阻抗50欧，信号线间距 $\geq$ 2倍线宽；

7. D0~D7、RE、WE相对于DQS做等长，控制 $\leq$ 300mil，使用过孔的数量尽量相同，务必保证走线参考平面完整。

8. VCC,VCCQ线宽不小于12mil。

9. 建议对RE、WE、DQS信号做包地处理，包地线通过过孔与GND平面连接。

10. 走线尽量避开高频信号。

11. VPS0和VPS1的电路连接需要参照相应NAND的DATASHEET作处理，具体连接可参考标案

# 06 ETHERNET

1. 变压器靠近RJ45座子摆放。

2. 以太网LED灯靠近座子摆放。

# 06 ETHERNET

3. RJ45及变压器下面所有层不铺铜，掏空。

4. 外挂100M和1000M PHY 差分对布线

- ( 1 ) 需要完整参考平面

- ( 2 ) 差分阻抗 $100 \text{ ohms} \pm 10\%$

- ( 3 ) 对内等长误差 $< 20\text{mil}$

- ( 4 ) 对间等长误差 $< 200\text{mil}$

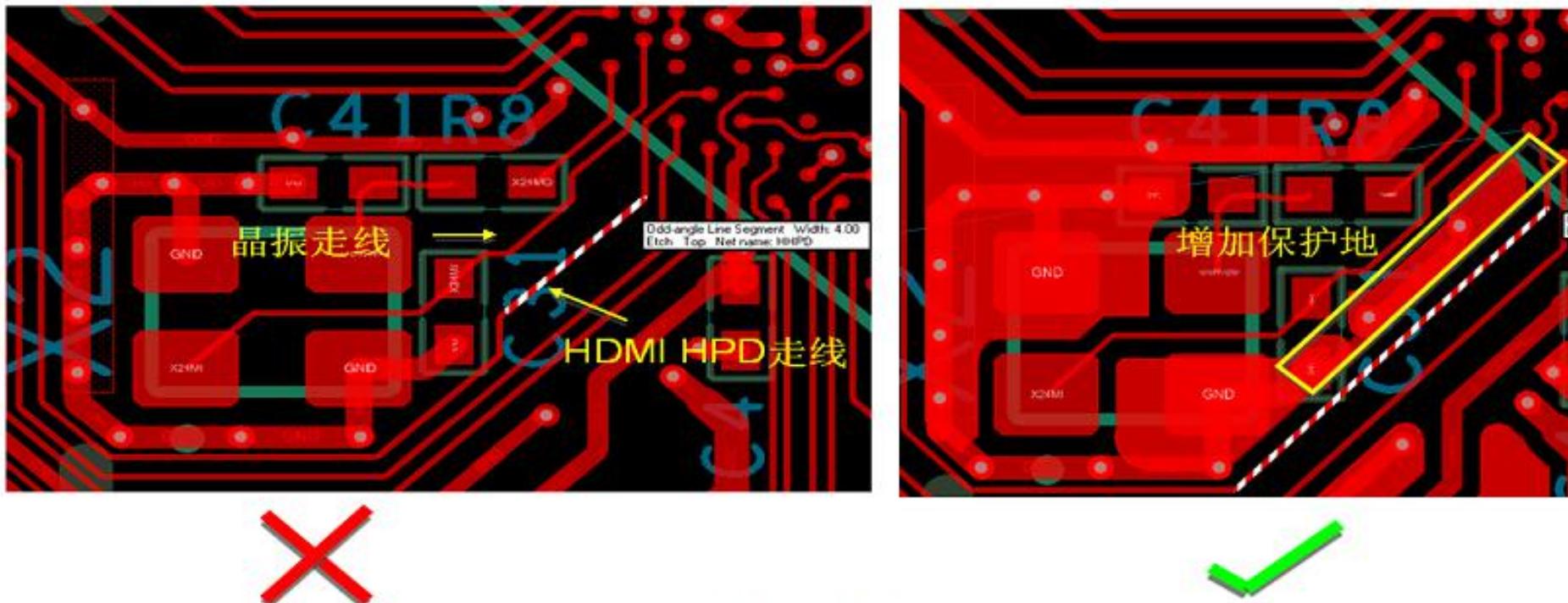

# 07 HDMI

1. PCB Layout时ESD器件靠近HDMI插座，见下图

2. HDMI座子以及信号走线的路径上，避免出现其他任何走线或电源板块，参考做法如下图：

# 07 HDMI

3. HDMI的差分信号线做等长差分线走线，差分线包地，差分阻抗要求 $100\text{ ohms} \pm 10\%$

4. HDMI差分推荐线宽和线距

$W=5.5\text{mil}$ ;  $C=9\text{mil}$ , (推荐)

$W=4.5\text{mil}$  ;  $C=8\text{mil}$  , (基本)

实际方案中，使用此推荐值可能无法做到 $100\text{ohm}$ 差分阻抗。此时应该在差分阻抗偏差不超出 $\pm 10\%$ 的基础上，尽量去保证线宽。

5. 差分对间保证 $3W$ 以上的间距；

6. HDMI信号线长度 $<3000\text{mil}$ ，差分线应该尽量顺直的从HDMI座子并行走到主控，不要刻意为了追求等长走“蛇形线”，需要保证HDMI差分线对内等长误差 $<200\text{mil}$ ，对间等长误差 $<1000\text{mil}$ ；

7. 差分走线过孔不超过2个，最好不打过孔。

# 07 HDMI

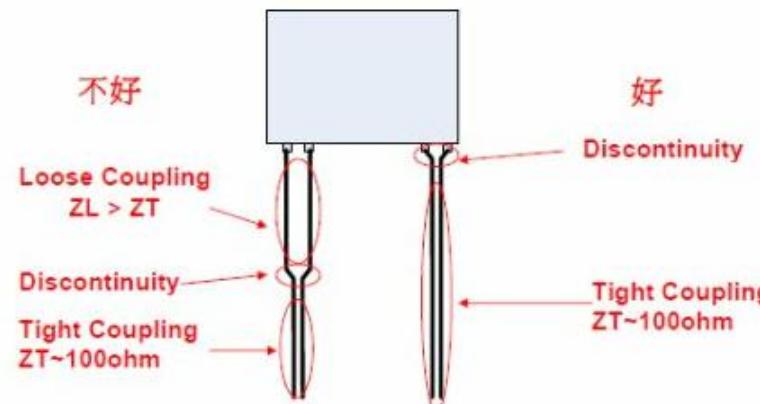

8. 尽量避免阻抗不连续，不要有90度转角的走线方式：90度转角的地方线宽较宽，阻抗会降下来，因此会产生不连续点；45度转角产生的不连续比较小，在可接受的范围内

9. HDMI左分线走线范围内最好不要有破坏差分走线的过孔，如下图

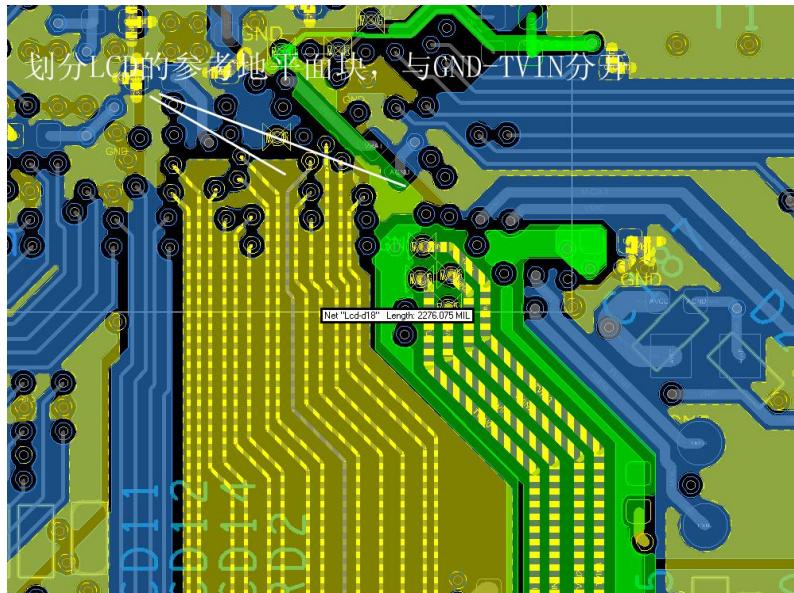

## 08 RGB/LVDS/DSI

1. 尽量满足3W原则，如不能，则至少要满足2W原则

2. CLK要做包地处理，同时要注意对包地打孔；

3. LCD线的参考平面要完整（尽量满足）；

4. VCC-PD的104滤波电容注意要尽量靠近IC端放置；

5. 如果LCD线有多功能复用，如LVDS功能，RGB功能加其他功能，尽量采用菊花链拓扑，减少分叉。

6. LVDS差分走线要求：

1080P：差分对内长度差10mil内，差分对之间的长度差180mil内。

720P：差分对内长度差20mil内，差分对之间的长度差450mil内。

阻抗要求：单端50欧姆，差分100欧姆。

# 08 RGB/LVDS/DSI

## 7. DSI差分走线要求：

- ( 1 ) 阻抗要求：单端50欧姆，差分100欧姆。

- ( 2 ) 差分约束：差分对内长度差10mil内，差分对之间的长度差160mil内。

- ( 3 ) 尽量保证走线的参考平面完整。

- ( 4 ) VCC-DSI处的104电容注意要尽量靠近IC端摆放

# 09 SATA

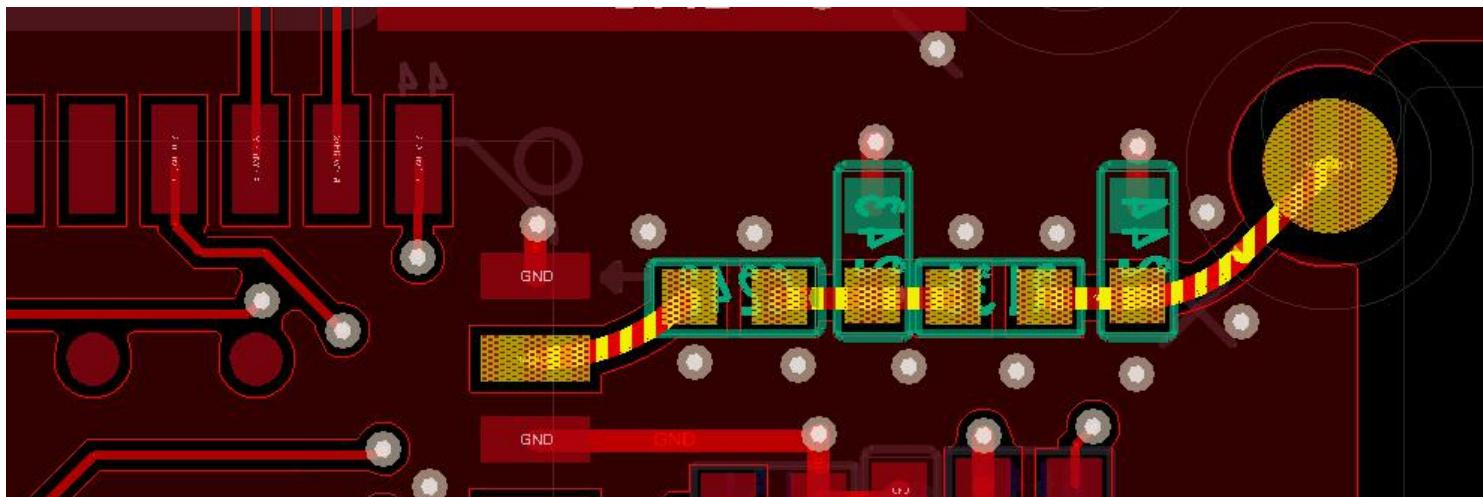

1. VDD25-SATA走线线宽8~12mil；

2. VDD25-SATA以及VDD12-SATA的去耦电容和滤波电容，需要靠近IC摆放；

3. SATA信号线TXP, TXM, RXP, RXM的串入电容，必须靠近connetor摆放；

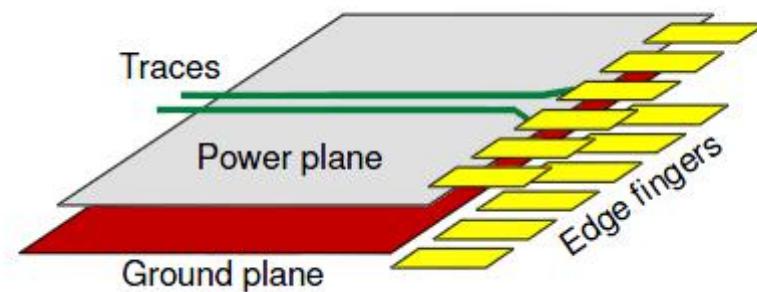

4. SATA信号线TXP, TXM, RXP, RXM，建议在表层走线，保证走线相邻层必须有连续完整的参考平面，并且参考面没有被分割；

5. TXP, TXM, RXP, RXM始终保证差分并排走线，差分阻抗为100欧，走线不能分叉；拐角的角度需保证大于135度；保证信号走线的长度控制在4000mil以内，走线的过孔不超过2个；

6. 建议优先考虑TXP, TXM, RXP, RXM走线，并与其它信号的间距大于10 mil，且避免走线走在器件的下面或者与其他信号交叉。

# 10 SDIO

1. CLK串接电阻靠近主控摆放。串阻与主控CLK连接走线距离≤300mil。

2. ESD器件靠近Device (卡座或Wifi模组) 摆放。

3. VDD网络上的电阻和电容网络靠近Device (卡座或Wifi模组) 摆放。

4. 卡座背面禁止放置插装器件，防止插装器件管脚干涉卡插拔。

5. 信号线走线要求：

- (1) 走线阻抗50欧；

- (2) 线间距不小于2倍线宽；

- (3) D0~D3相对CLK等长控制<500mil；

# 10 SDIO

6. 信号线走线参考平面完整；

7. CLK做包地处理，包地通过过孔与GND平面连接。如果不能包地则保持线间距 $\geq$ 3倍线宽。

8. VDD走线宽度不小于12mil；

9. 卡座管脚走线先与ESD器件相连后，再连其它器件；

10. 走线尽量避开高频信号。

1. 走线间距尽量满足3W原则。

2. 尽量保证走线的参考平面完整。

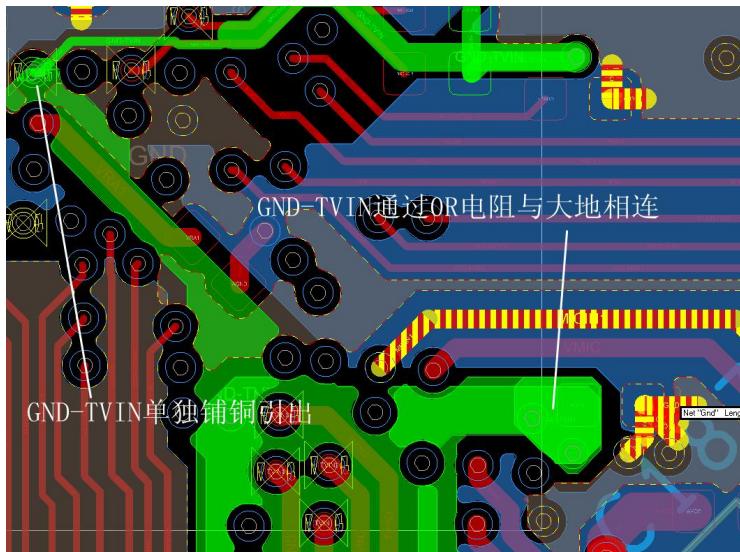

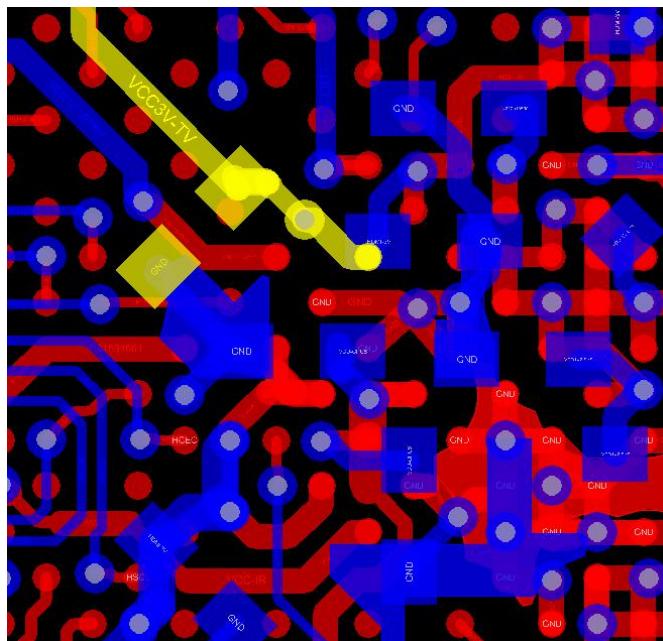

# 12 TVIN

1. 去耦电容靠近电源PIN放置，距离PIN距离不超过200mil。

2. VCC-TVIN走线及其过孔远离高速信号，远离高速信号的过孔。尤其是并行LCD信号。

3. VCC-TVIN走线线宽不少于20mil。

4. GND-TVIN从IC端引出单独分配一片覆铜，铜宽不小于50mil。通过0R电阻与系统GND平面连接。

# 12 TVIN

5. GND-TVIN的回流路径注意要避开LCD信号的GND回流路径。

6. VRP-TVIN, VRN-TVIN去耦电容靠近PIN的位置放置，距离PIN距离不超过200mil，走线不小于10mil。

7. 走线及过孔远离高速信号，远离高速信号的过孔。尤其是并行LCD信号。

8. VRP-TVIN、VRN-TVIN采用差分走线。

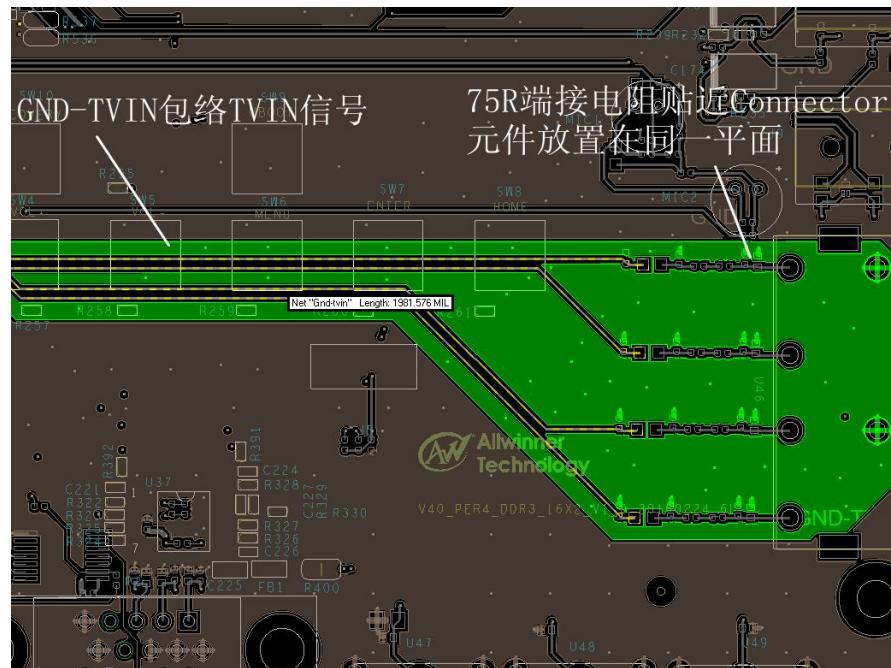

# 12 TVIN

9. 走线及过孔远离高速信号，远离高速信号的过孔，尤其是并行LCD信号。

10. 75R端接电阻贴近Connector放置。信号通道上的元件放置在同一走线层。

11. TVIN信号线采用37.5ohm阻抗匹配，采用GND-TVIN包络。

# 13 TVOUT/CVBS/VGA

1. 每路TVOUT需要电流为45mA，可根据方案TVOUT输出确定VCC-TVOUT线宽

|             | 1路TVOUT方案 | 4路TVOUT方案 |

|-------------|-----------|-----------|

| VCC-TVOUT线宽 | 20mil     | 40mil     |

2. VCC-TVOUT电容最好放置在主控PIN正下方，距离PIN距离不超过200mil

# 13 TVOUT/CVBS/VGA

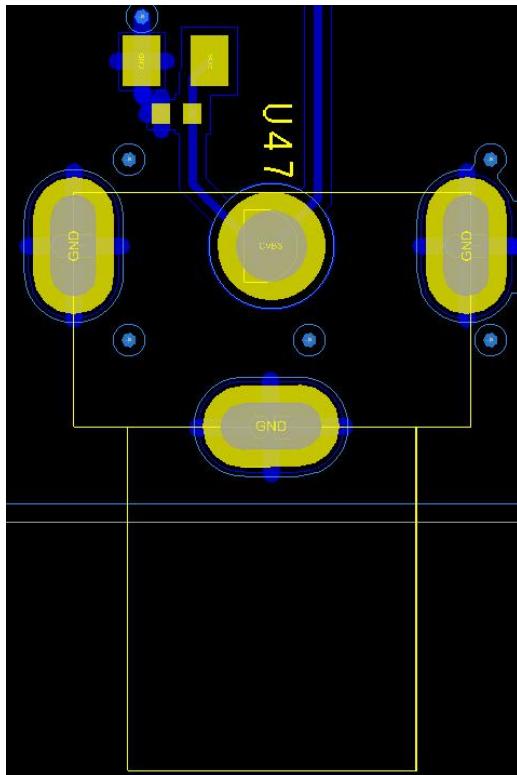

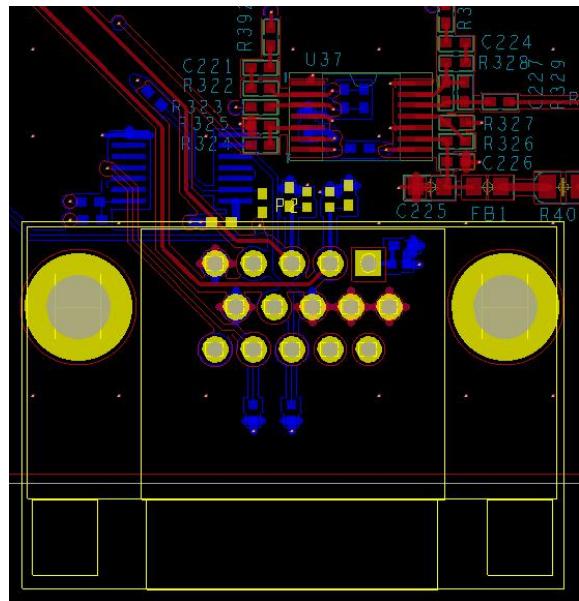

3. 75ohm终端电阻和ESD器件以及滤波电阻电容靠近座子摆放，如下

(1) 1路TVOUT CVBS方案

# 13 TVOUT/CVBS/VGA

## ( 2 ) 3路TVOUT VGA方案

### (3) 4路TVOUT YPbPr+CVBS方案

#### 4. TVOUT信号线需要参考完整地平面

## 5. TVOUT信号线采用37.5ohm阻抗匹配

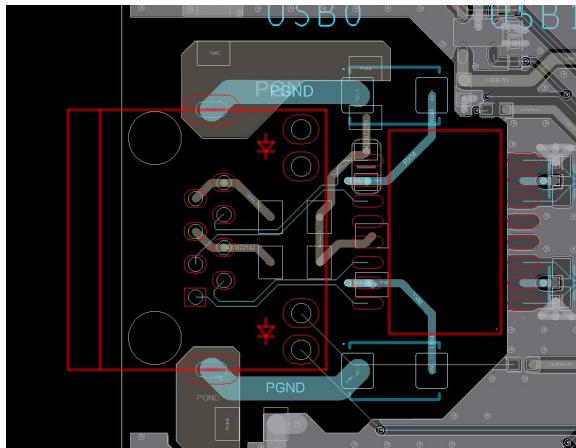

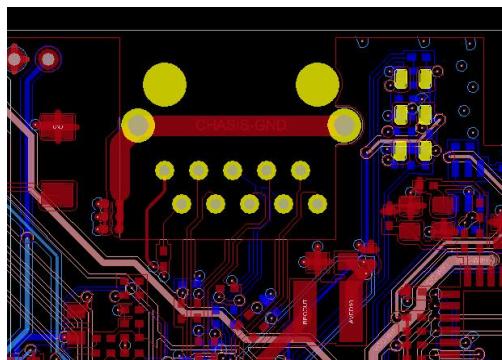

# 14 USB

1. VCC3V3-USB走线线宽8~12mil；

2. USB-5V电压到USB SOCKET的 VBUS PIN的回路，电流最高可达1A，线宽需要控制在40mil以上，见图

3. VCC3V3-USB的去耦电容和滤波电容，需要靠近IC摆放；

4. USB SOCKET的去耦电容，应靠近SOCKET的VBUS PIN摆放；

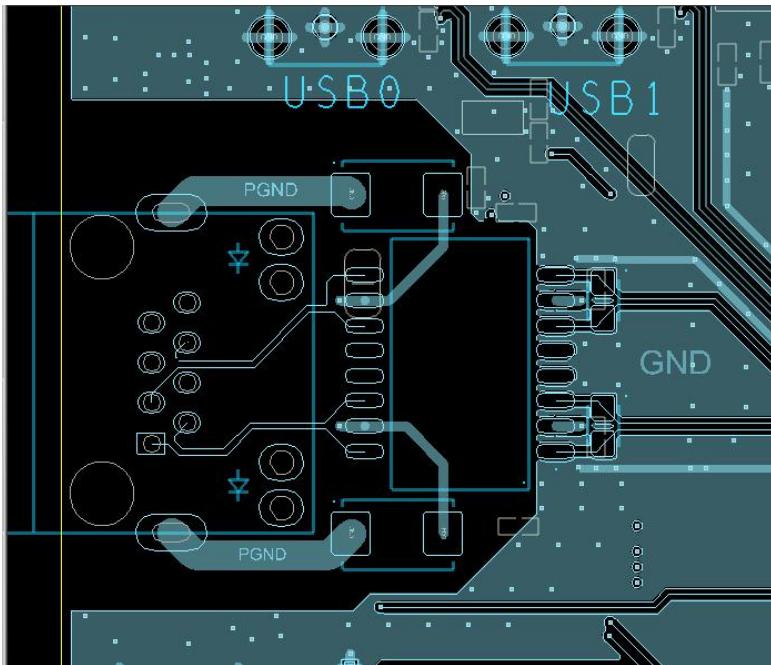

# 14 USB

5.为了获得较好的ESD防护能力，TVS器件需要靠近USB 座子摆放，见图

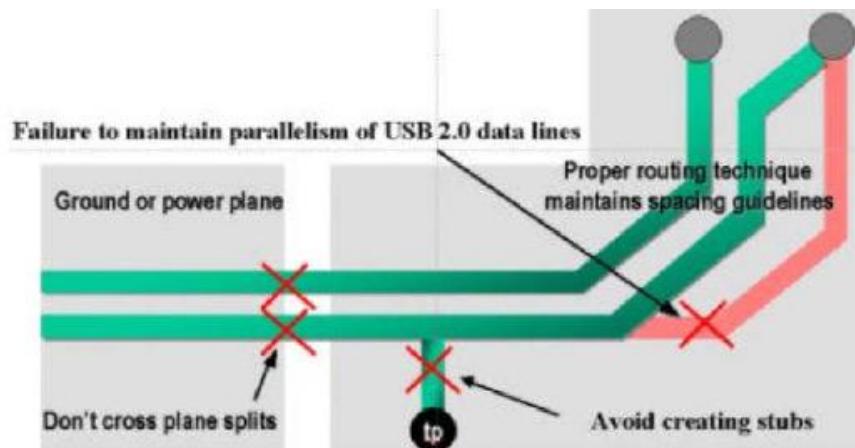

6. USB信号线DM、DP，建议在表层走线，保证走线相邻层必须有连续完整的参考平面，并且参考面没有被分割；

# 14 USB

7. DM、DP始终保证差分并排走线，差分阻抗为90欧，走线不能分叉；拐角的角度需保证大于135度；保证USB走线的长度控制在4000mil以内，走线的过孔不超过2个；

8. 建议优先考虑DM、DP走线，并与其它信号的间距大于10 mil，且避免走线走在器件的下面或者与其他信号交叉。

9. DM、DP为高速信号线，并接的TVS要求低容值，否则影响数据传输，以小于或等于4pF为宜。

10. DM、DP连线与USB SOCKET要一一对应，不要反接。

# 15 WIFI/BT

1. 模组尽量靠近天线或天线接口。远离电源、DDR、LCD电路、摄像头、马达、SPEAKER等易产生干扰的模块

2. 天线馈线控制50ohm，左右包地并沿途多打GND过孔。为了增大线宽减少损耗，通常馈线相邻层挖空，第3层需要完整参考地。

3. 合理布局天线馈线的匹配电容电阻，使馈线平滑，最短。无分支，无过孔，少拐角。

# 15 WIFI/BT

4. 如使用PCB走线作天线，请确保天线走线附近区域完全净空，净空区大于50mm<sup>2</sup>。天线本体至少距周围的金属1cm以上。

# 16 GPS

1. GPS电路位置，远离电源、DDR、LCD电路、摄像头、马达、SPEAKER等易产生干扰的模块，间距至少20mm。

2. TCXO对温度敏感，尽量远离PMU、CPU、PA、散热器等发热体。TCXO靠近GPS BB摆放。

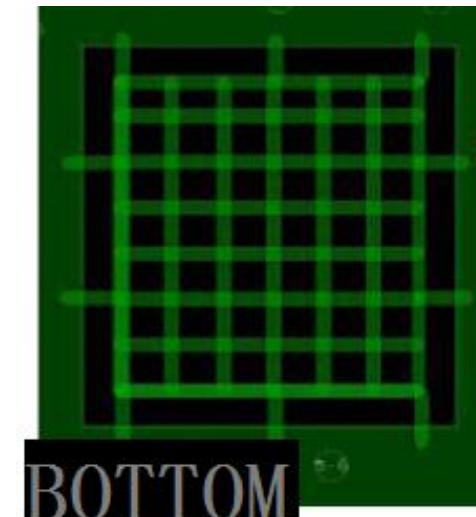

3. 为减少温度影响，TCXO下方各层都必须净空（Bottom层除外），Bottom层以“网格形状”覆地，并且“网格形状”入地点要少一些。

4. TCXO接地管脚单点入地

# 17 THERMAL

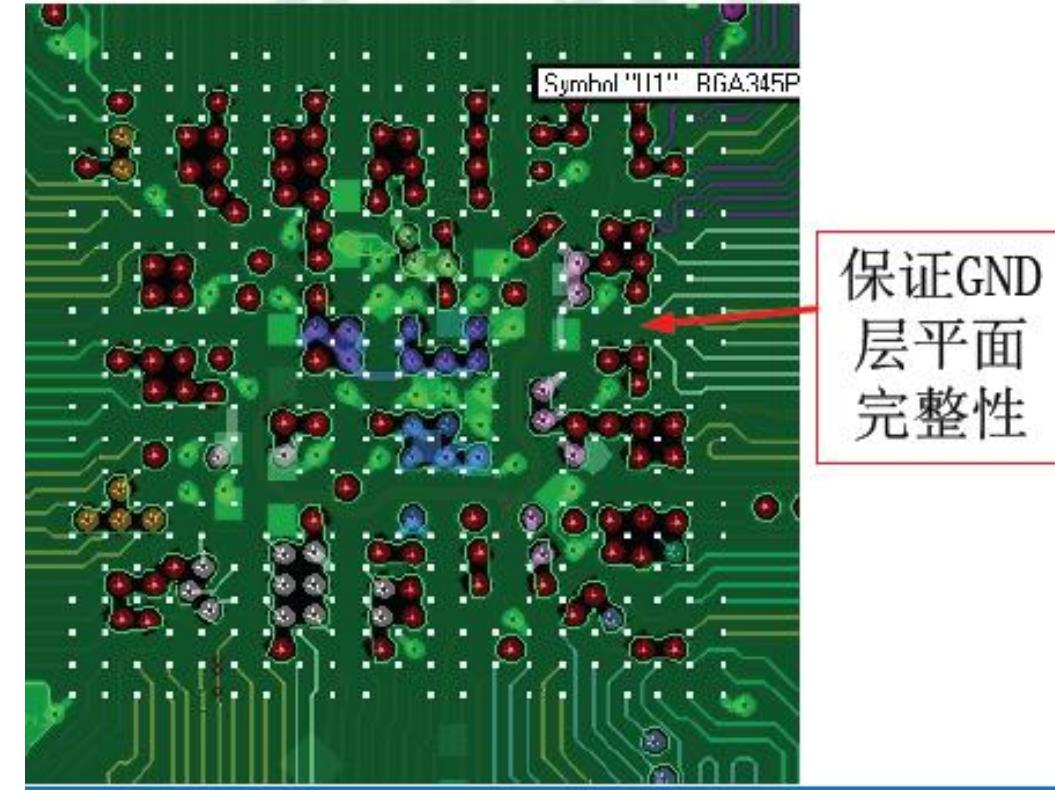

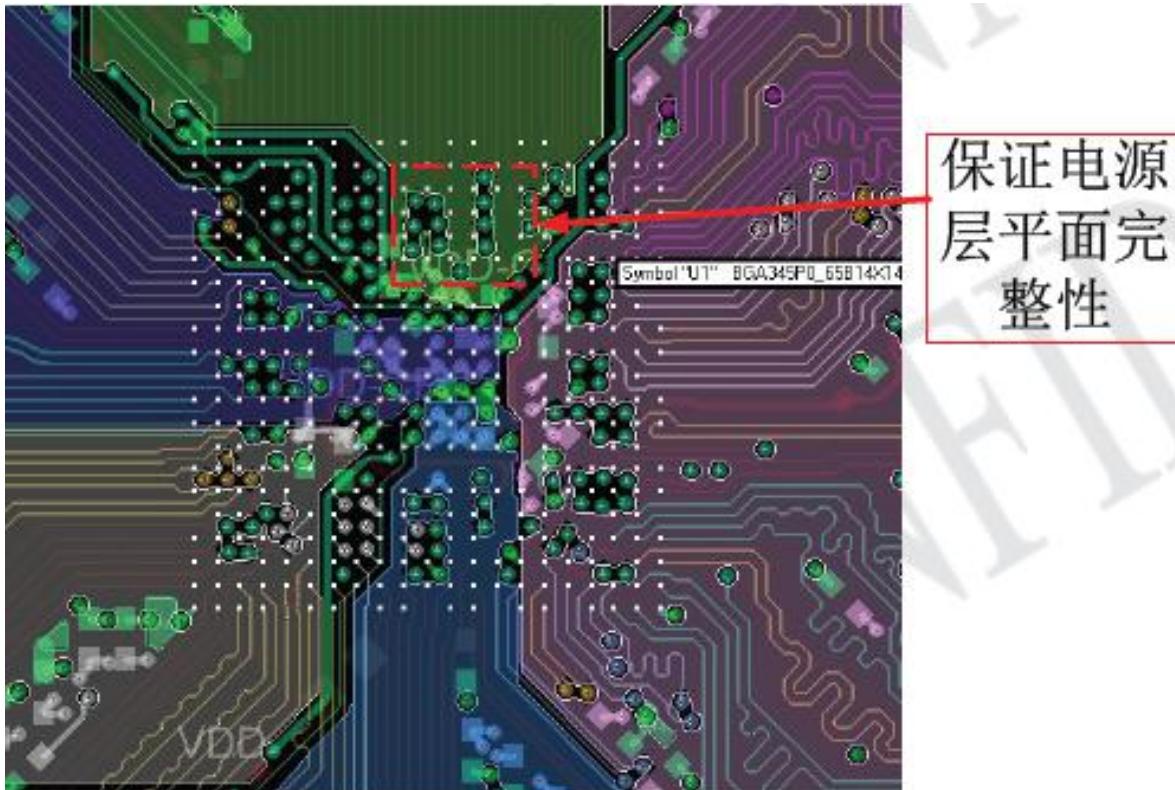

1. 保证GND平面和电源层各电源部分平面的完整性，以保证热量的平摊

# 17 THERMAL

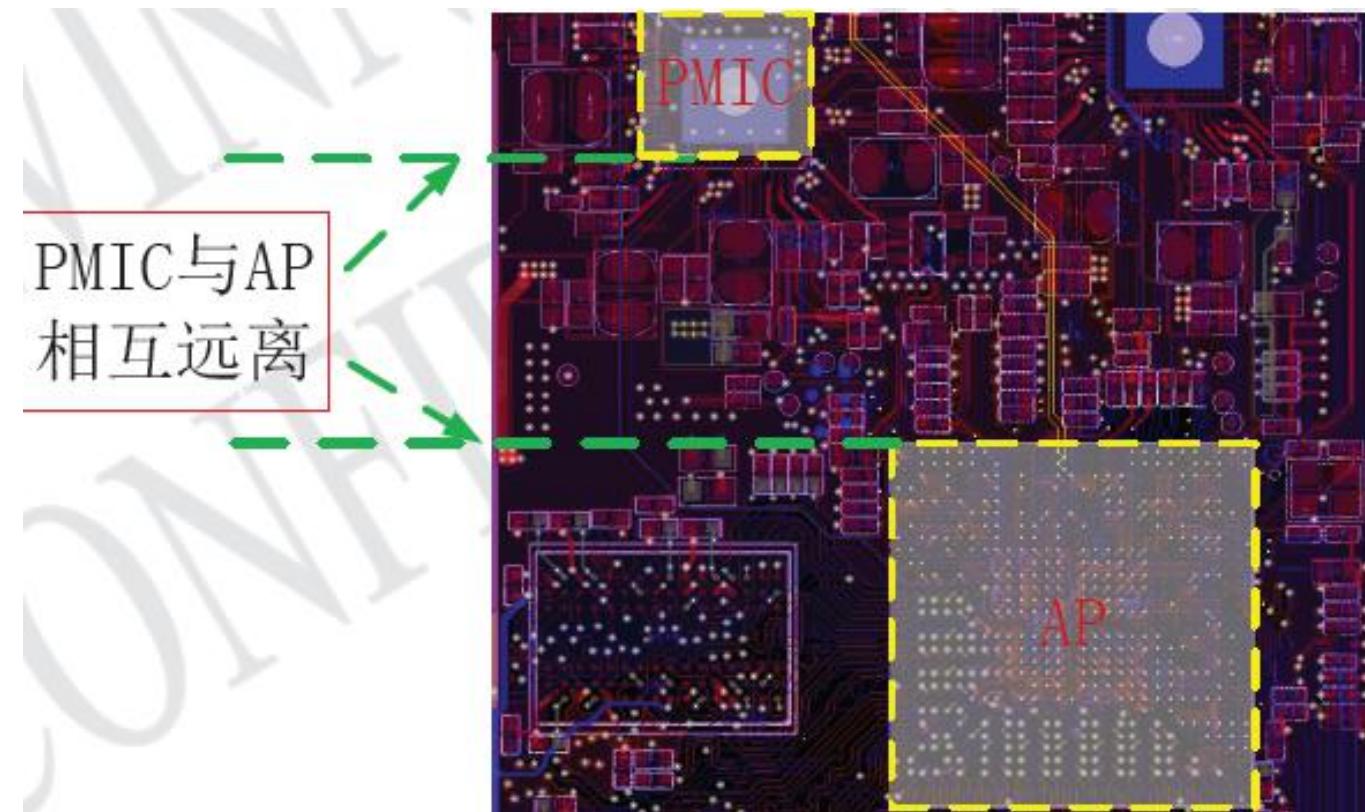

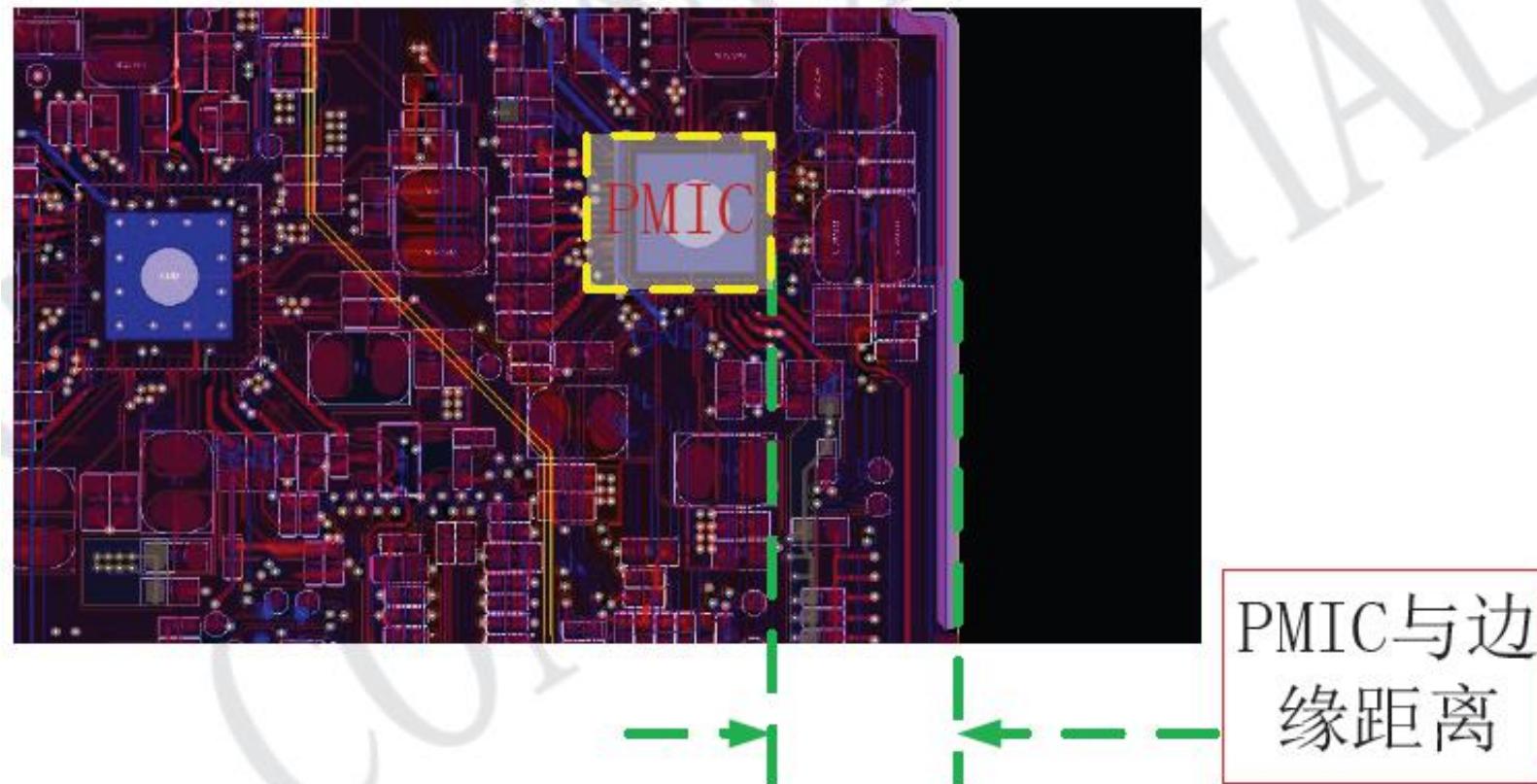

2. PCB板上较大功率器件均匀摆放，避免多个热源靠在一起；AP与PMIC/Modem/PA的距离不小于20mm。

# 17 THERMAL

3. AP尽量放在PCB靠中间的位置，PMIC/PA等较大功率器件摆放位置离PCB边缘不能过小（不小于10mm）

# 17 THERMAL

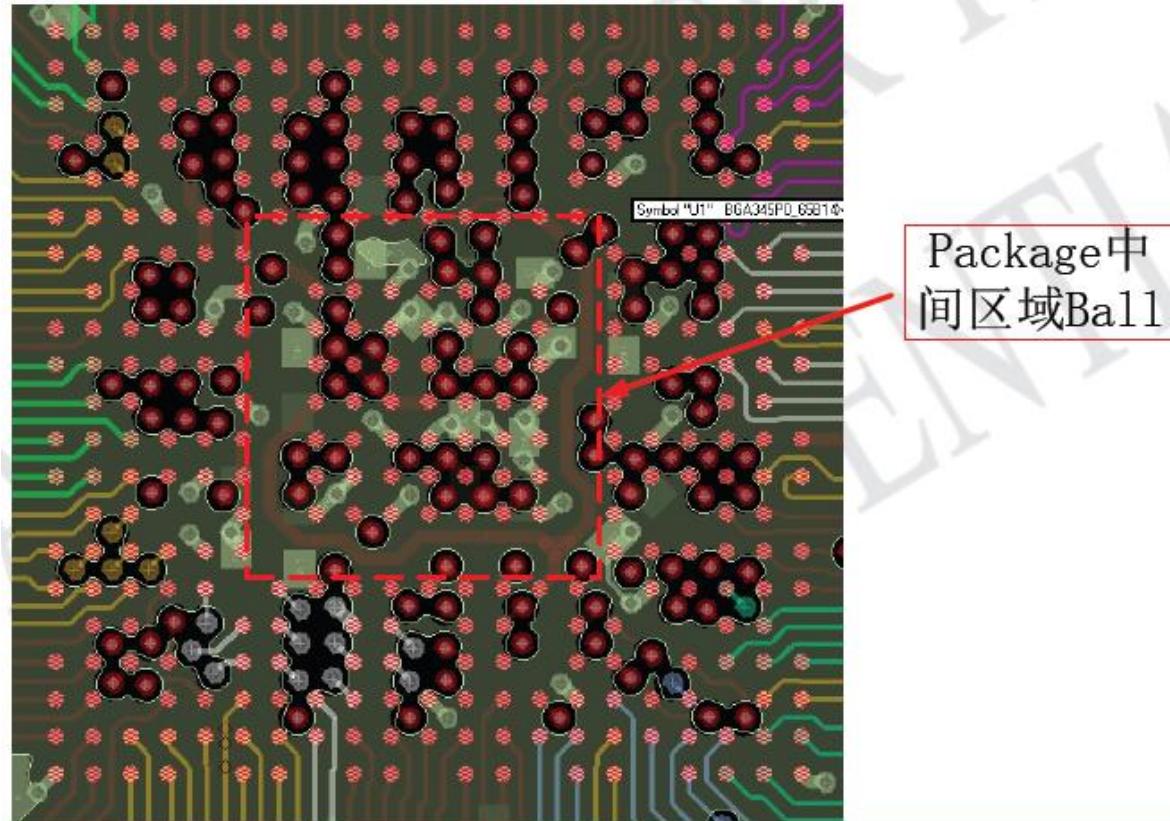

4. Package中间区域的Ball是把热传导到其他平面层和底部的主要途径，需要保证与Ball连接的Via数量

# 17 THERMAL

5.保证GND , VDD-CPU , VDD-SYS , VDD-DRAM的每个Ball不少于一个Via。

6.在PCB Layout空间允许的情况下，在PCB背面铺保留一层完整的铜皮利于散热。

# 17 THERMAL

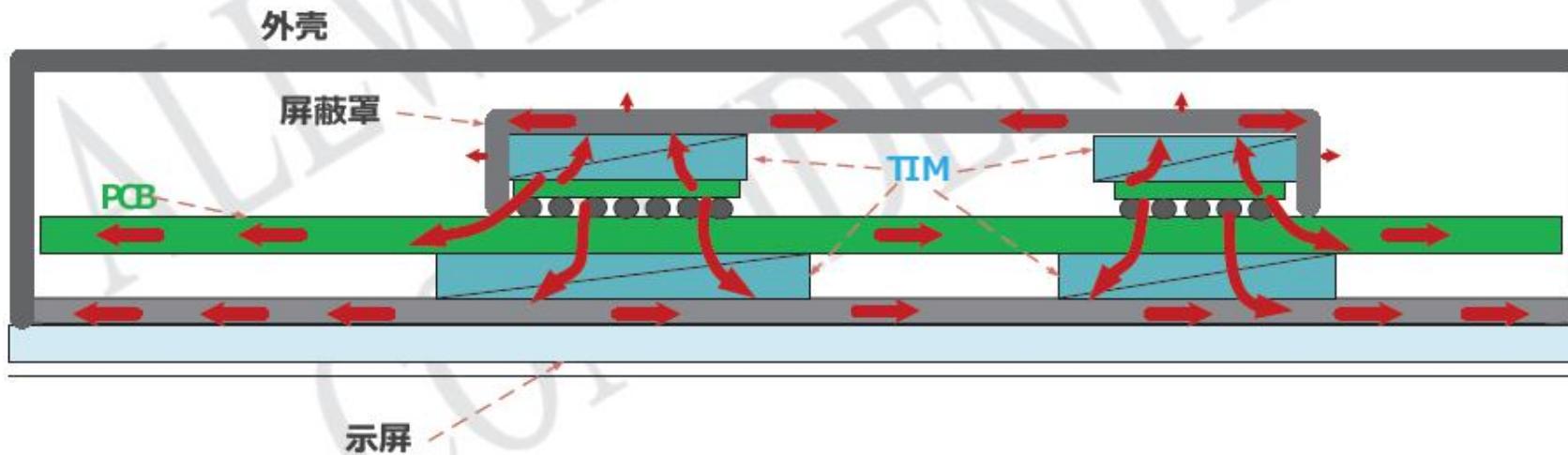

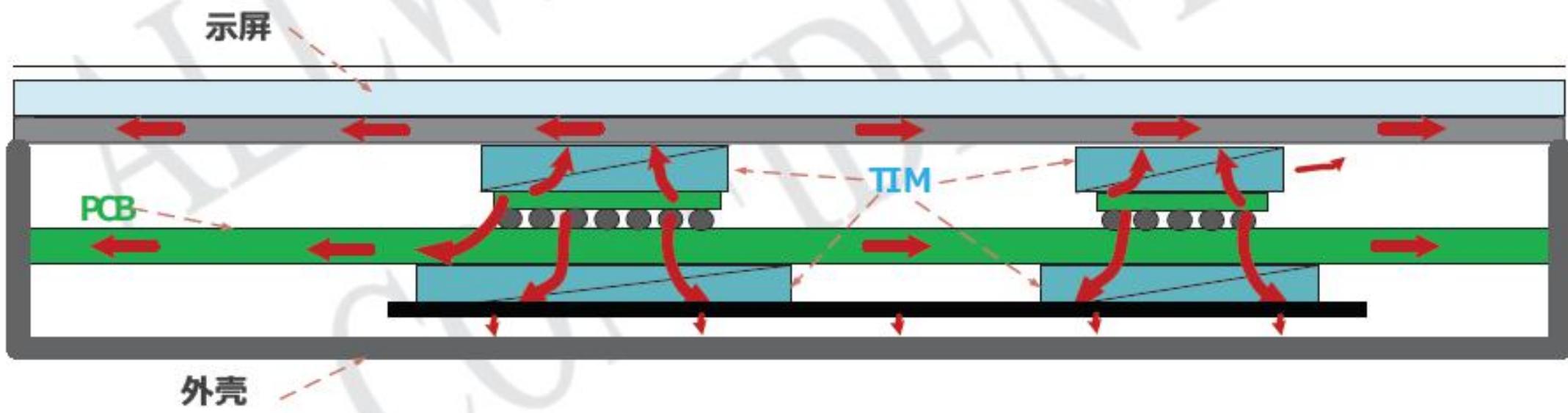

## 7. 整机安装：显示屏在PCB背面。

PCB背面：

1. 屏上面有一层大面积金属层，可以充分利于该金属层进行导热。

2. 金属层与PCB层之间放TIM ( Thermal Interface Material ) 材料。

PCB正面：

1. 如果AP和PMIC外有金属屏蔽罩，可以用TIM紧贴AP和金属外壳以降低热阻。

# 17 THERMAL

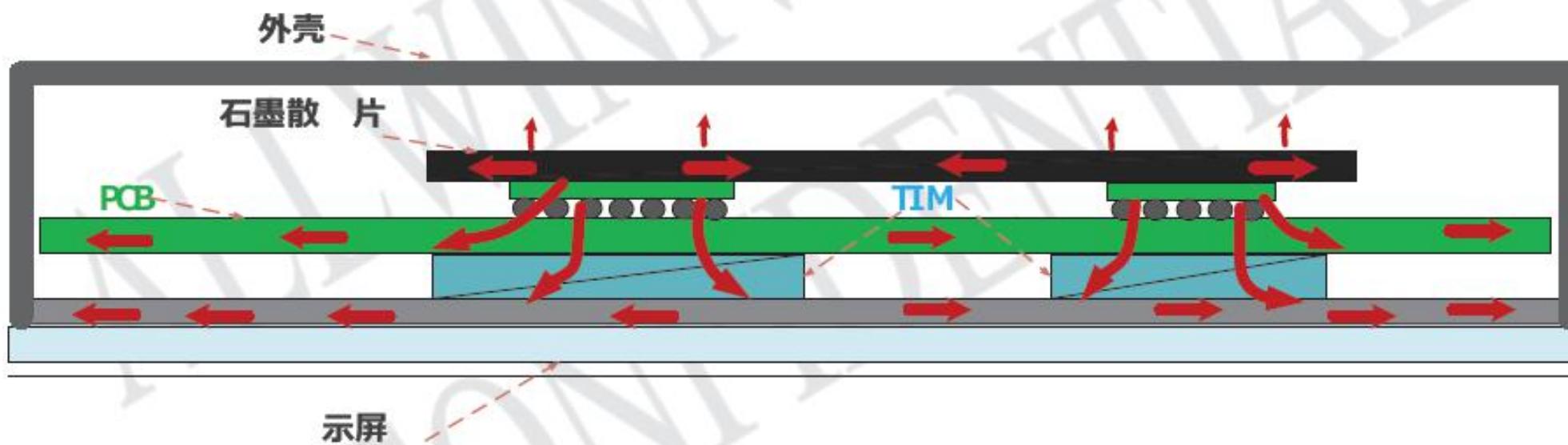

8.整机安装：显示屏在PCB背面。

PCB正面：

1. 如果AP和PMIC外围没有金属屏蔽罩，可以用石墨散热片贴在AP和PMIC上进行散热。

# 17 THERMAL

9.整机安装：显示屏在PCB正面。

PCB正面：

1. 屏上面有一层大面积金属层，可以充分利于金属层进行导热。

2. 金属层与AP之间放TIM材料。

PCB背面：

1. 在AP和PMIC的PCB背面放TIM材料，后可以在TIM上加散热片，例如0.2mm铜片和纳米材料组

1. PCB层叠设计必须保证不少于1L完整的GND平面，所有的ESD泄放路径直接通过过孔连接到这个完整的GND平面；（完整GND平面有利于电荷的快速转移）

2. 地保护环

PCB板四周画上一条宽度不小于0.5mm(20mils)的地保护环且尽可能多铺地；

保护环铜皮不能覆盖绝缘材料（例如绿油）；

保护环需要通过过孔与GND平面相连，每10mm的距离不少于2个过孔；

保护环不能形成闭环，每隔一段距离，可以留下一个0.5~1mm的缝隙；

敏感信号不能与保护环相邻，与保护环的距离不小于0.25mm(10mils)；

与保护环相邻的非敏感信号到保护环距离不小于0.2mm(8mils)。

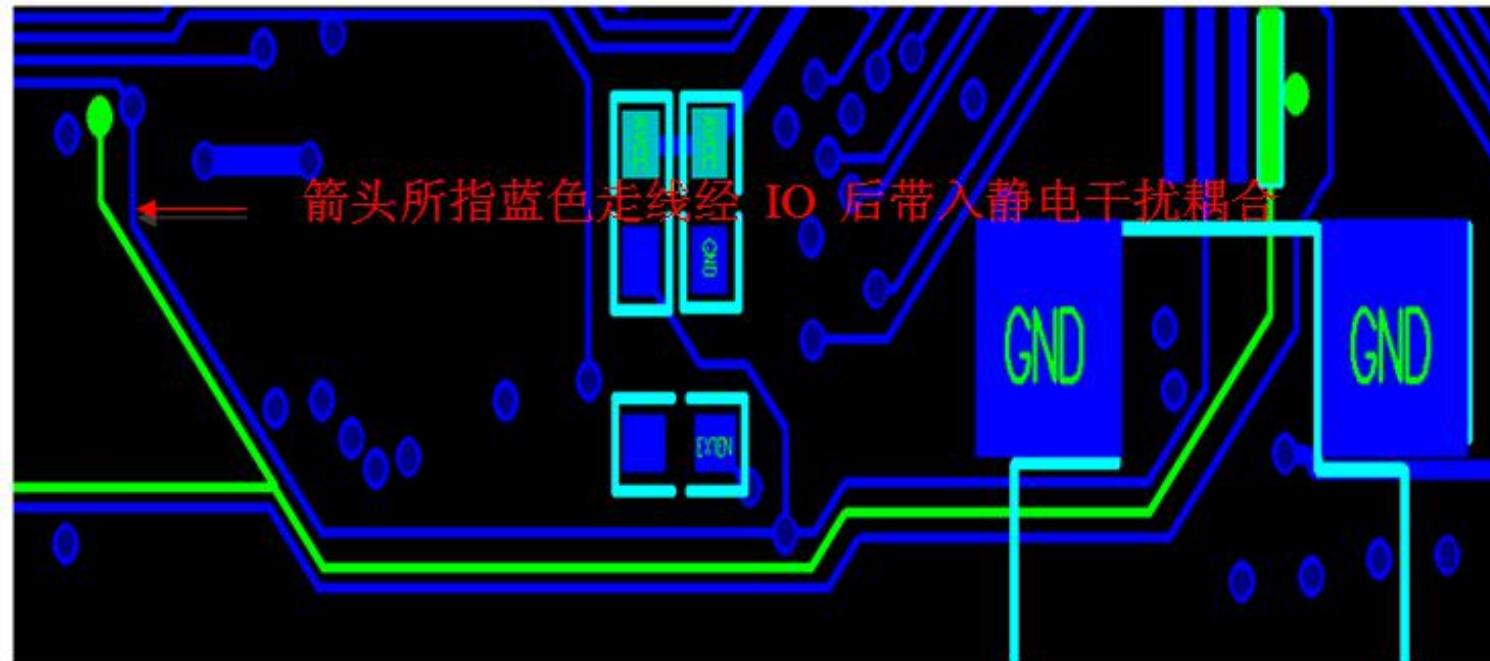

3. IO保护地下方尽量不要走线，在必须走线的情况下建议走内层（防止静电能量耦合到走线后造成二次污染）。

4. 关键信号 (RESET/NMI/Clock等) 与板边距离不小于5mm, 同时必须与走线层的板边GND铜皮距离不小于10mils; (避免空气放电和GND平面电磁耦合)。

5. CPU / DRAM / 晶振等ESD敏感的关键器件, 离外部金属接口的距离不小于20mm, 如果小于20mm, 建议预留金属屏蔽罩; 并且距离其他板边不小于5mm; (避免金属连接器对内部器件放电)。

6. POWER平面要比GND平面内缩不少于3H (H指POWER平面相对GND平面的高度)。压缩第三层不必要的电源走线面积, 尽可能多的铺GND。

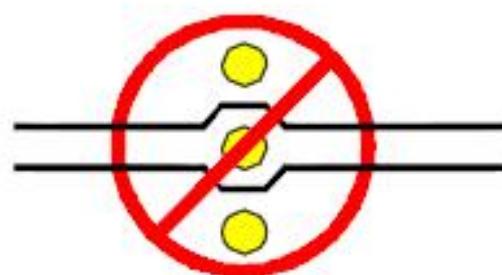

7. 关键信号 (RESET/NMI/Clock等) 尽量避免与外部接口信号 (USB/HDMI/SD/HP等) 或经过IO附近的走线相邻并行走线; 如果不可避免, 相邻并行的走线长度不超过100mils; (避免外部信号的电磁耦合)。

# 18 ESD

禁止并行走线示例一

# 18 ESD

禁止并行走线示例二

# 18 ESD

8. Reset信号建议增加1nF电容接地，电容靠近主控摆放；电容接地端需用过孔加强连接；Reset走线需要全程用GND走线保护；

9. 对于模组上的reset信号，需在模组上靠近芯片管脚的位置增加1~100nF电容接地。

- 10.无论外部接口信号还是内部信号，走线必须避免多余的桩线（一端无电气连接的走线）；（避免天线效应，放电和接收电磁辐射）。

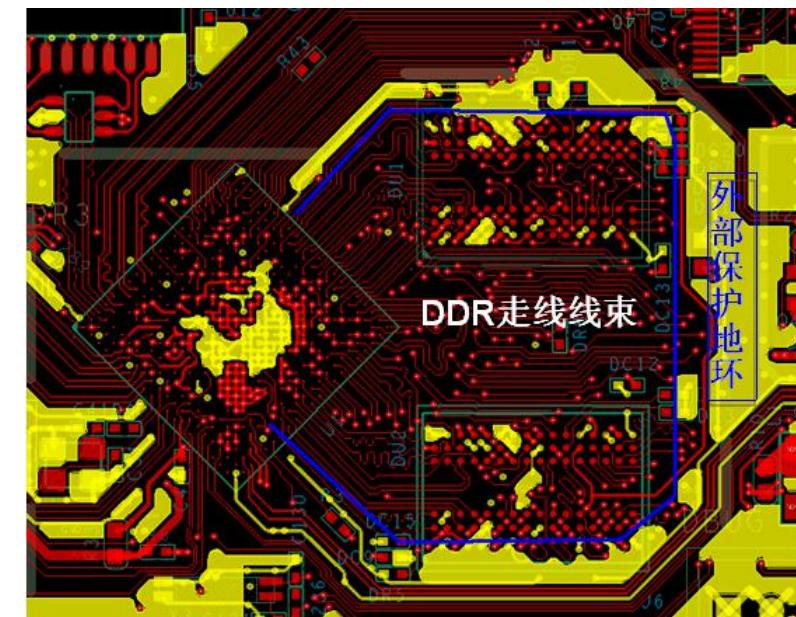

11. DDR线束四周建议用GND保护（屏蔽静电干扰）。

# 18 ESD

12.对于4层板，DDR的走线推荐采用SPSG层叠结构，即第一层走信号，第二层走电源，第三层走信号，第四层走GND（屏蔽静电干扰）。

# 18 ESD

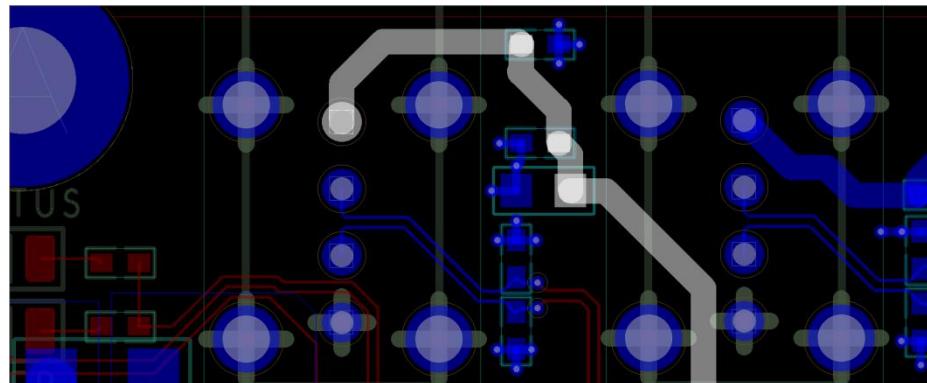

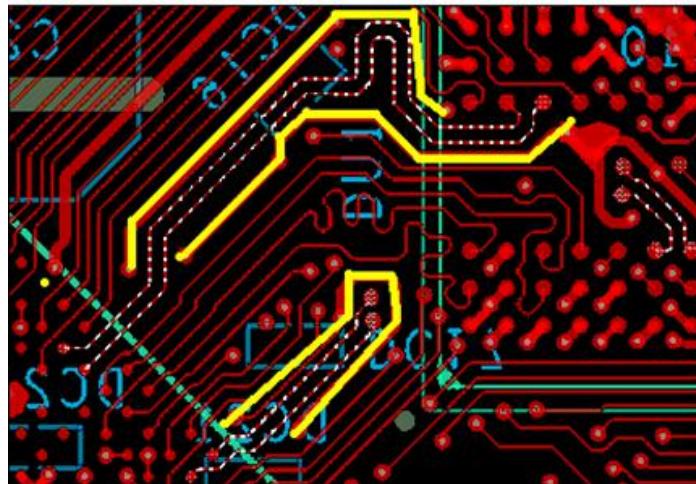

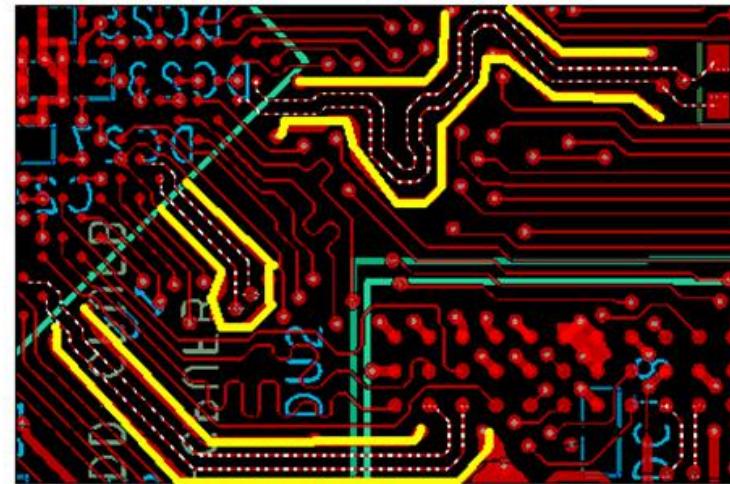

13. DDR Clock差分对/DQS差分对全程走线用GND走线保护，GND走线的过孔间隔要求小于等于400mil ( 屏蔽静电干扰 )。

DQS0/1包地示例

DQS2/3、CLK包地示例

14. 必须保证外部连接器 ( USB/HDMI/SD ) 金属外壳接地良好，在板边直接通过过孔连接GND平面，每个GND焊盘与GND平面之间的连接过孔不少于3个。

# 18 ESD

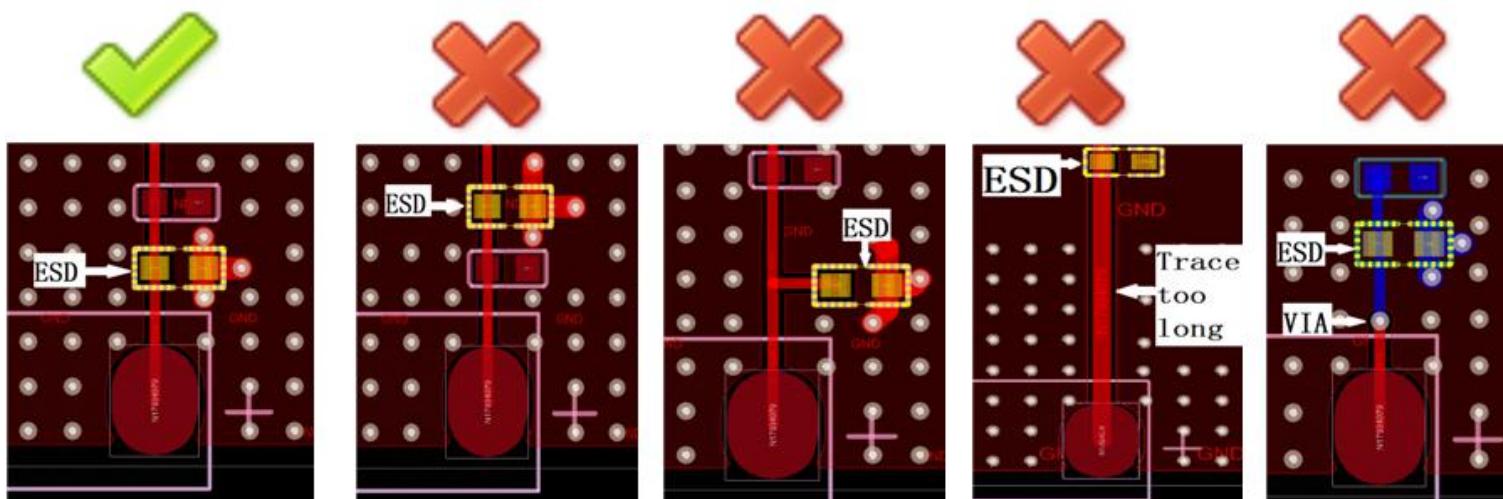

15. 外部接口信号 ( USB/HDMI/SD/HP ) 必须连接外部ESD器件，进行ESD保护。

如下图所示，外部接口信号ESD器件放置位置尽可能靠近外部连接器，与连接器间避免过孔；ESD器件接地端直接通过过孔连接到GND平面，而且过孔数量不少于3个；从外部接口进来，必须最先看到ESD器件；ESD器件的信号端与外部信号端必须尽可能短，尽可能宽，建议直接搭接在信号走线上。

# 18 ESD

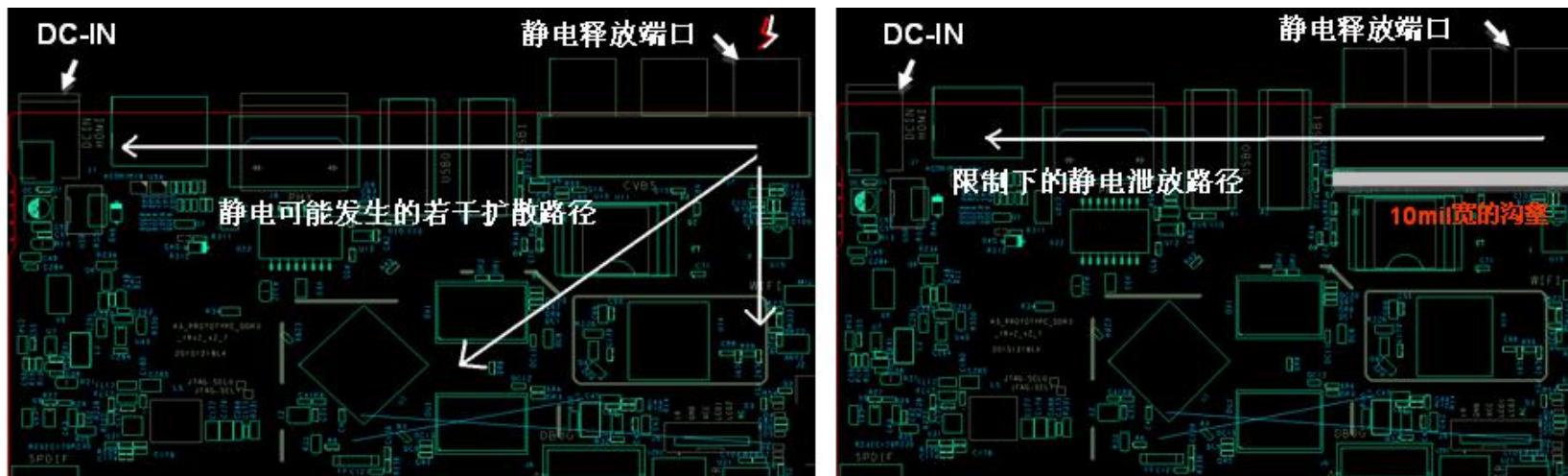

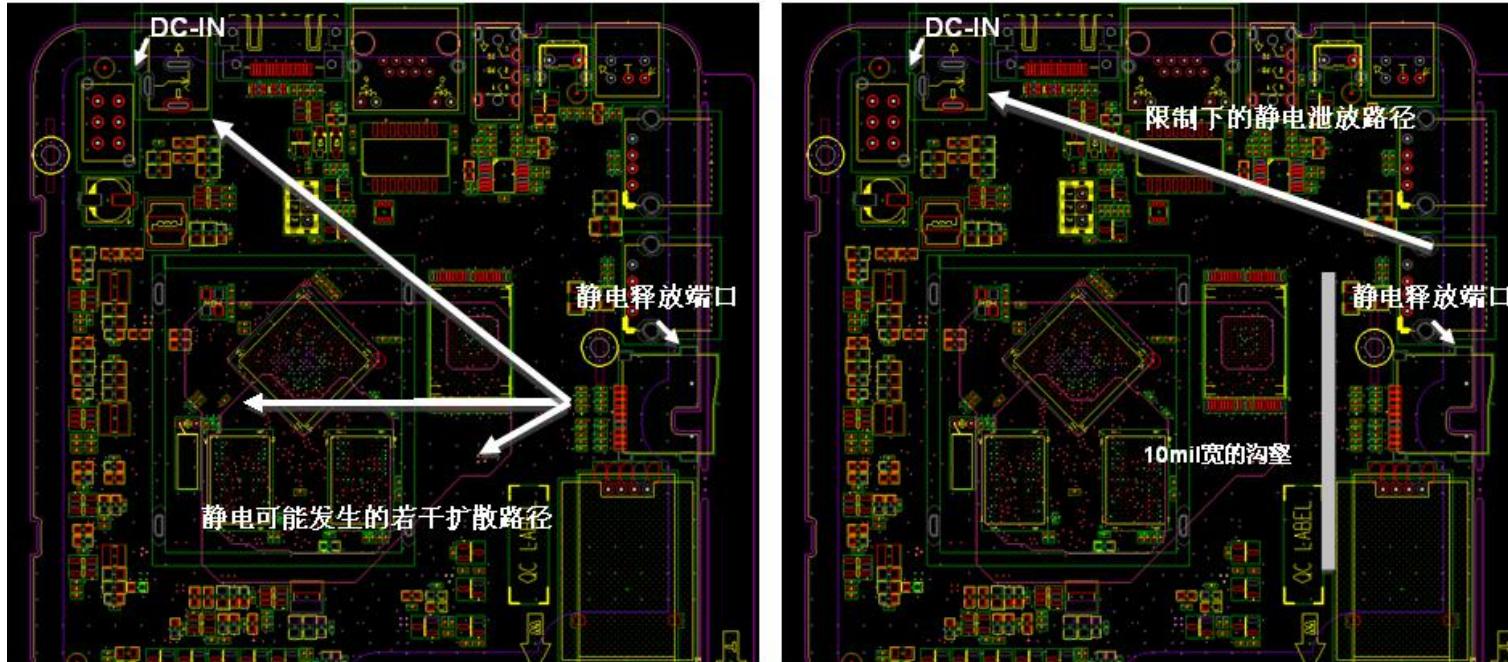

16. 有些IO由于布局关系，远离静电泄放路径（如DC-IN端口）或者与静电泄放路径形成对角线关系（静电泄放路径经过主控下方极易造成干扰）。这类IO容易在静电测试时造成系统失效。建议于此类IO的GND附近在PCB所有层割一段10mil宽的沟壑，以引导静电按照设计路线泄放，阻止能量串入主GND。

割壕沟示例一

# 18 ESD

割壕沟示例二

# 18 ESD

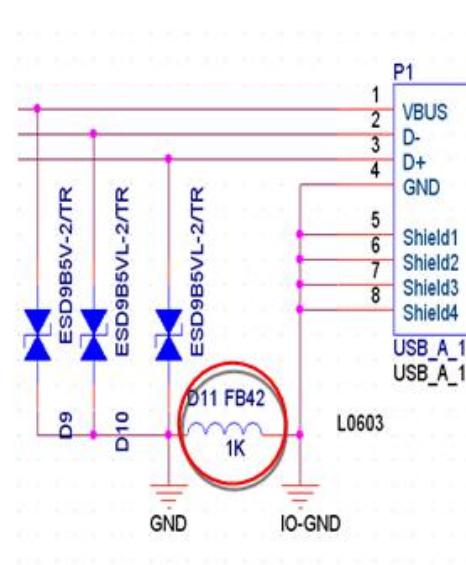

16.对于部分ESD整改难度较大的IO，可将IO GND独立出来，与主GND用磁珠连接以防止静电能量进入主GND（需在信号质量可接受的范围内）。

# 18 ESD

17.如果系统包含了其他子板（如按键子板，天线子板），这些子板上的ESD器件建议放在主板上靠近座子的位置。

# 18 ESD

- 18.建议在PCB板双面四周均匀留出多个不小于25mm<sup>2</sup>的GND裸露铜皮（此铜皮直接通过过孔与GND平面相连），并通过导电棉与金属平面相连接。

- 19.如果结构允许，建议增加屏蔽罩，对关键电路进行屏蔽，同时必须保证屏蔽罩的各边良好接地；（避免屏蔽罩电荷积累，对内部信号放电）。

# 19 PMU

1. 推荐采用4层(顶层，S1,S2,底层)，顶层或底层放置元器件，顶层和第三层走功率(电源)路径。

第二层为地层，底层以信号优先，其次是难以在顶层和第三层布的功率路径。4层以上的，可以单独为信号使用一层。

2. 对于PMIC的使用面积充分的应用，PMIC及电感、电容等主要器件放置在同一层，地层紧邻PMIC放置层，比如PMIC放置在第一层，则地层设置在第二层；对于PMIC使用面积特别紧张的，可以把电感电容等大器件放至在PMIC对面一层的正下方。

3. 通常用以下几种方式评估路径：

1mil的铜厚(包含沉铜厚度)，则1A电流需要预留28mil的线径宽度。

$DCR\ (mohm) = \frac{\text{长度}}{\text{宽度} \times OZ}$ , 例如长度是宽度100倍，1OZ铜厚，则DCR为1mohm，0.5OZ则是2mohm。

一个8mil的过孔通流能力为500mA。

# 19 PMU

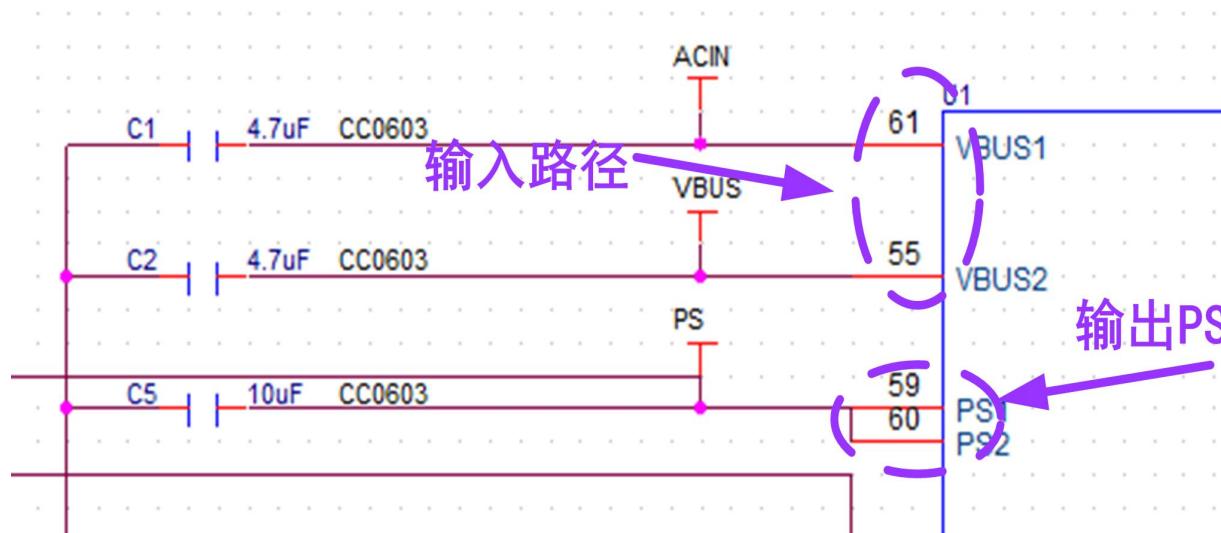

4. IPS在功能上是把PMIC外部的电，如充电器，电池，外部电脑等通过VBUS或者ACIN导入到PMIC中，经过智能管理，通过PS输出，PS输出的电既可以送给系统中的其它功能供电如液晶屏，保护电路等，也可以给PMIC的DCDC, LDO，辅助功能供电。这里有几点值得注意：

# 19 PMU

5. VBUS或者ACIN的路径尽量用铺铜，宽度尽量大，最少应保证可以流过最大的规格电流；应至少保证有84mil的宽度来流过 $I_{in\_max}=3A$ 的电流。但是通常VBus和ACIN从较远的connector端引入，要求从引入端到芯片的pin， $DCR \leq 0.04\Omega$ 。这就要求在宽敞的地方尽量铺宽VBus和ACIN，要求长度 $\leq$ 宽度的40倍，而不是局限于84mil宽度。

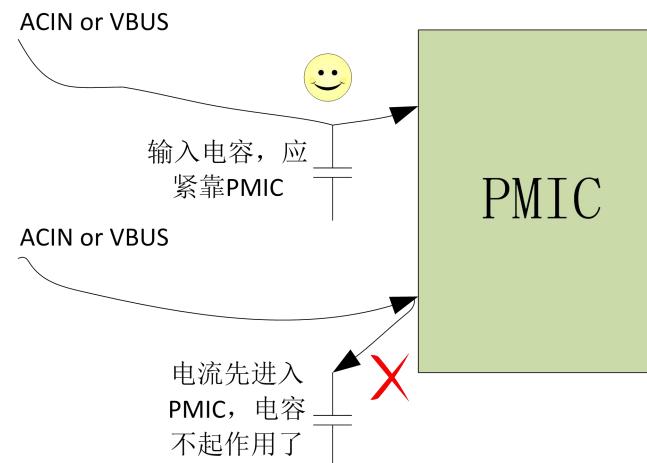

6. 输入滤波电容尽量靠近VBus和ACIN pin，使外部来的电先通过电流滤波后再进入到PMIC。如有过孔到电源层的过孔不少于4个；

# 19 PMU

7. IPS模块的输出端一般为PS pin，它的滤波电容尽量靠近这个PS Pin，走线尽量宽，铺铜，到电源层的过孔不少于4个；

8. PS也为PMIC的其它模块供电，如给Charger提供输入，给DCDC，LDO提供输入，因此PS最好有一个电源平面。减小PS到DCDC，LDO的阻抗，尽量用打孔到电源平面，铺铜的方式。

9. 电感如与PMIC相接，保证电容位置的前提下，尽量靠近PMIC的LX pin。线宽保证电流需求即可，不要太宽。

10. 如果PMIC 有PGND pin, 则要注意PGND与GND层的连接。通常PMIC的PGND紧挨着DCDC，charger的LX或者VIN。

# 19 PMU

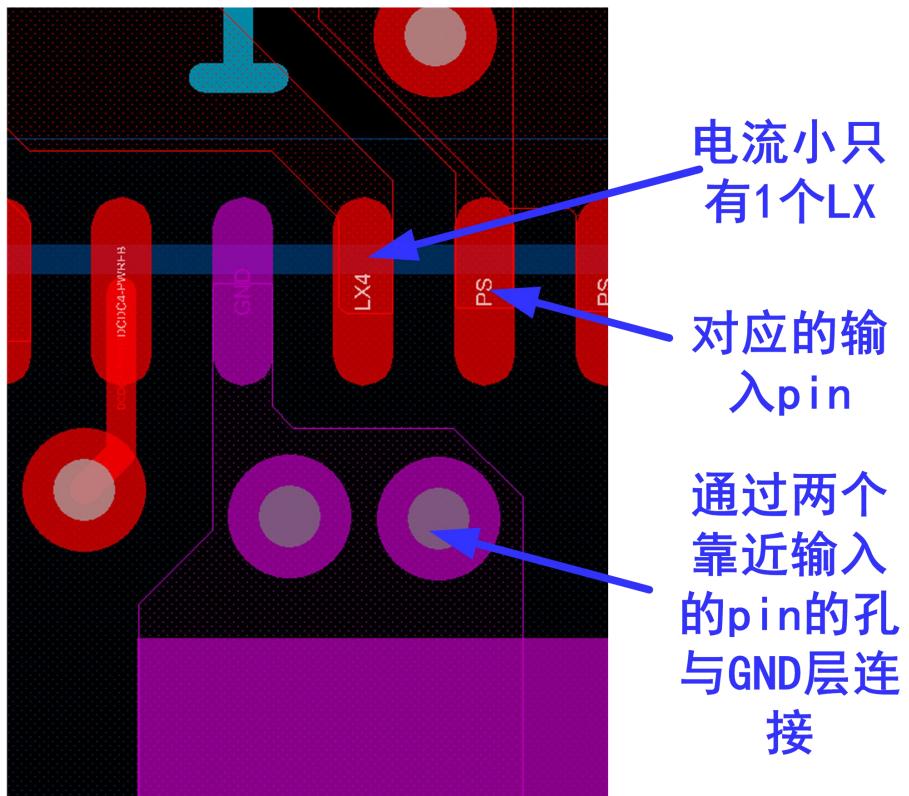

11. 对0~1.5A的buck, DCDC, charger, boost, 通常只有1个LXpin。其PGND pin与电容的连接是通过打孔到地层。打孔的位置可以在如下图所示地方，可以在PMIC内打孔。

# 19 PMU

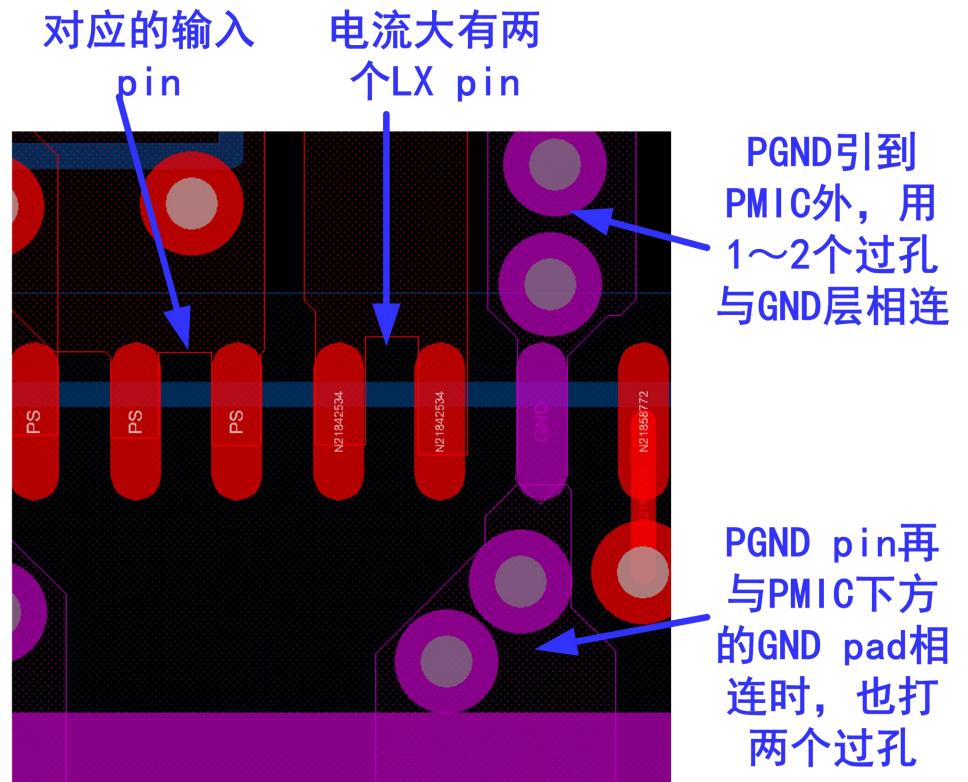

12. 对1.5A ~ 3A的buck, DCDC, charger, boost, 通常有2个LXpin。其PGND pin与电容的连接是通过打孔到地层。打孔的位置可以在如下图所示地方。在PMIC内和外都打孔。如果有地方PMIC外打2个孔，如果没有地方则打至少1个孔

# 19 PMU

13. 对于电流>3A的buck, DCDC, charger, boost, 通常有>2个LXpin。其PGND pin与电容的连接是通过打孔到地层。

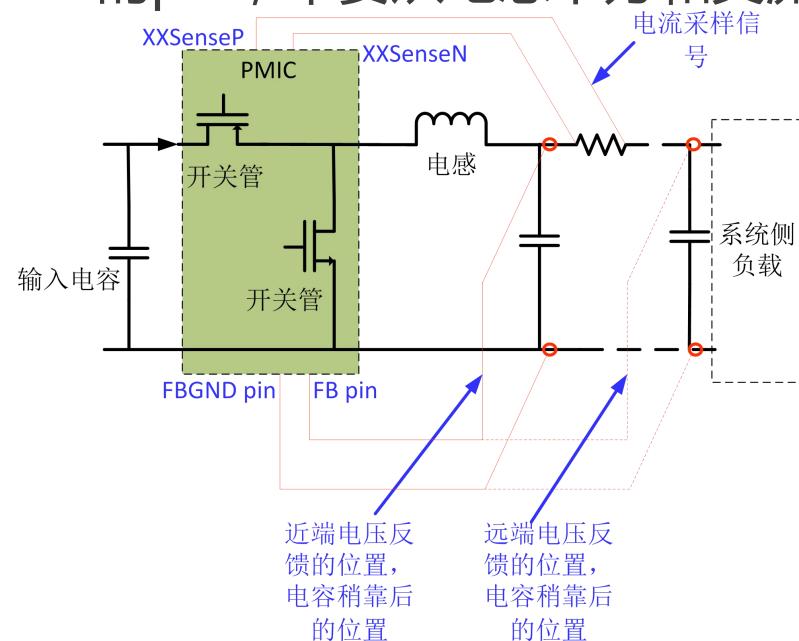

14. DCDC敏感信号主要有电流反馈线, 电压反馈线, 驱动线, 和自举电路线。一般信号线

(1) 电流反馈线, 采用差分走线, 从采样电阻的一端开始到PMIC的pin, 不要从电感下方和交流路径的下方走线, 一般用4~10mil即可

# 19 PMU

- (2) 电压反馈线，输出电压经过电容滤波后，紧挨电容取点，用4~10mil的线引入PMIC即可，最好不要从电感下方，交流路径下方，或者紧挨CLK之类的跳变信号。建议CPU，GPU，SYS，DRAM供电时，从远端反馈。如果SOC有反馈pin则连接至反馈pin，如果没有反馈pin，则连接至远端反馈电容两端。反馈线从底层信号层走线，沿其电源平面一起走到负载。

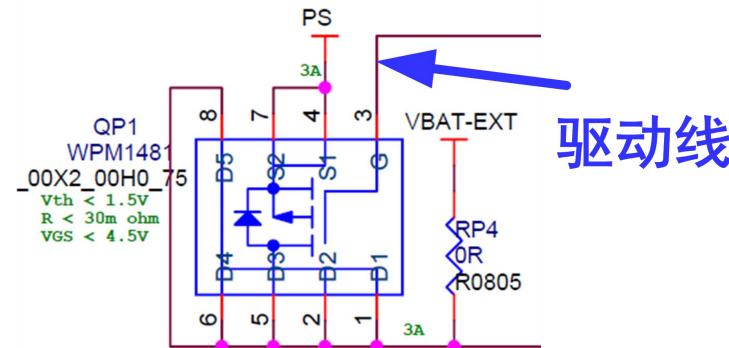

- (3) 驱动线，一般是PMIC给MOS作为驱动的信号。用4~10mil的线，从信号层引入到MOS的gate即可，gate附近打孔到信号层。要区分这个驱动信号线常态为固定电平还是跳变电平，如果是跳变的，不要让它受到其它跳变信号干扰；如果是固定的可以不像跳变信号那么严格要求。

# 19 PMU

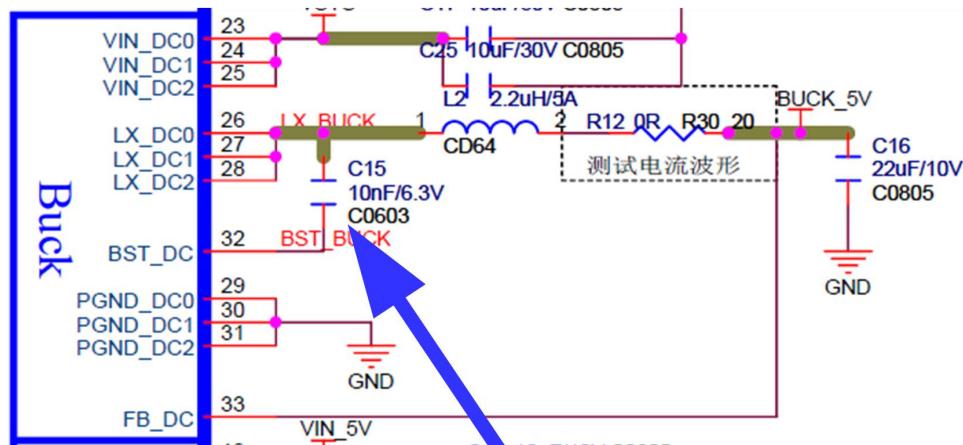

(4) 自举驱动供电线路，一般用作上下管的驱动供电。电容的取点应靠近电感端的LX端；如一般以BST命名的pin外接的电容一端连接LX时，取点应靠近电感取点。用10mil即可。

自举供电电容

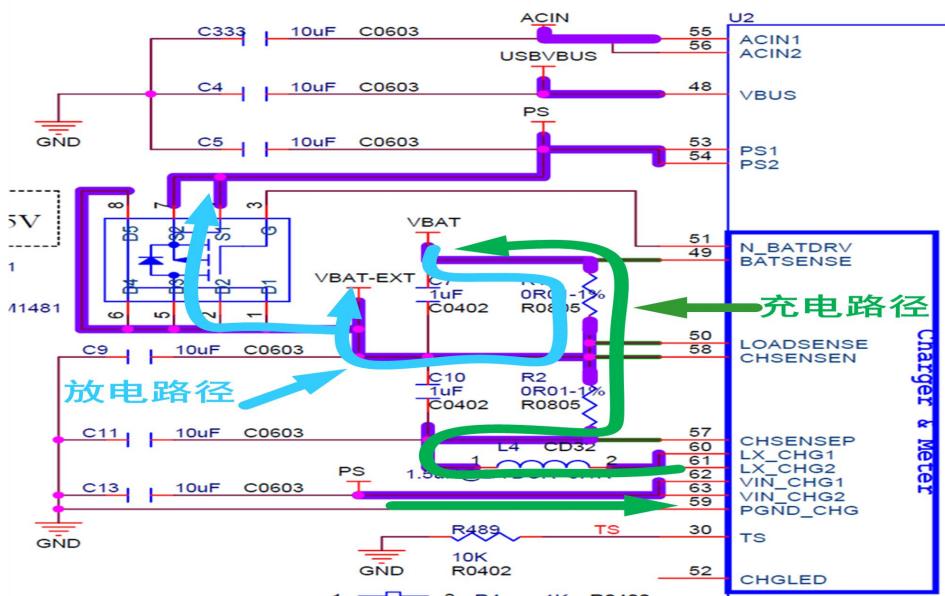

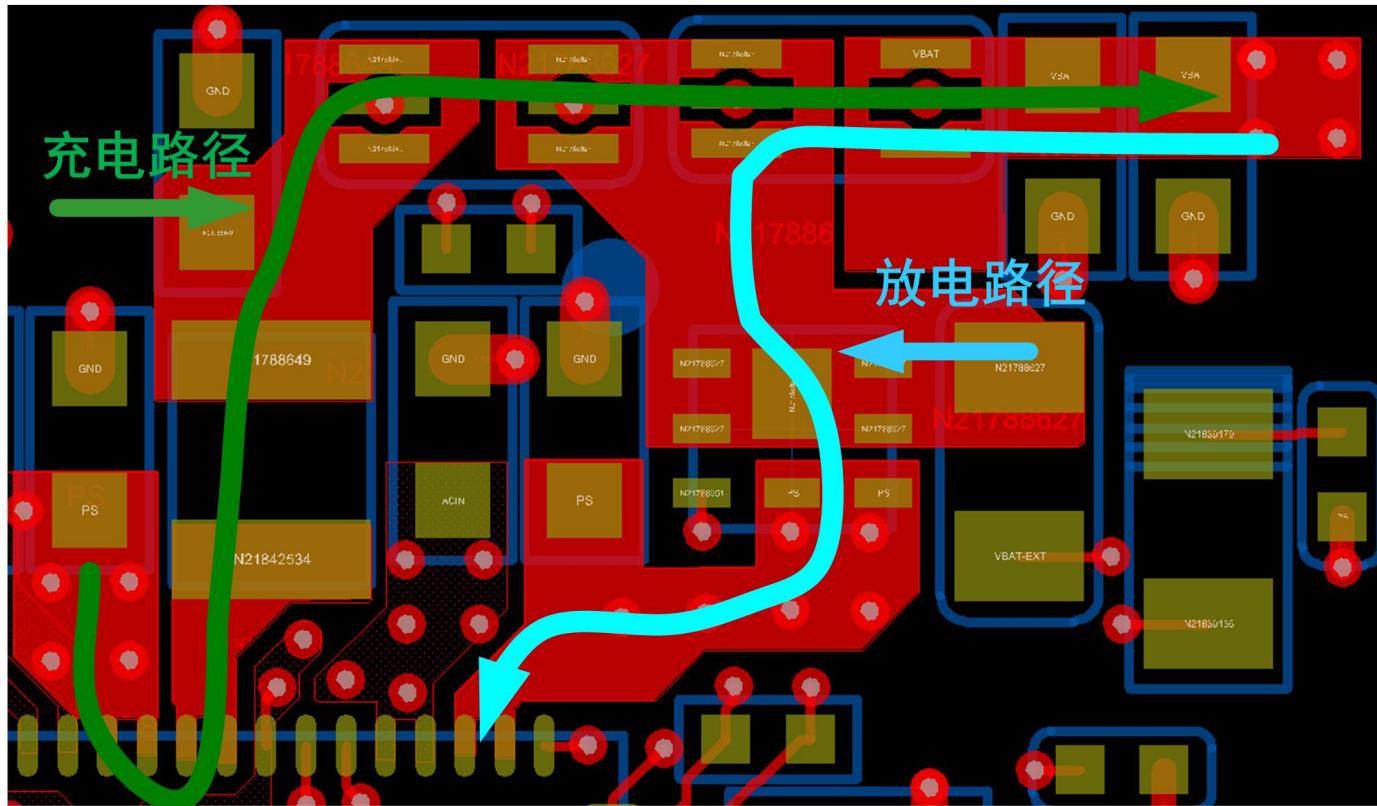

15.充电路路径为PS->VIN\_CHG->LX\_CHG->电感->采样电阻->BAT，尽量采用铺铜，路径短。如下图绿色箭头线。

放电路径为VBAT->采样电阻->外部PMOS->PS，尽量采用铺铜，路径短。如果有单独的放电采样电阻，原则与充电采样电路相同。如下图蓝色箭头线。

充放电路径如下图所示。

# 19 PMU

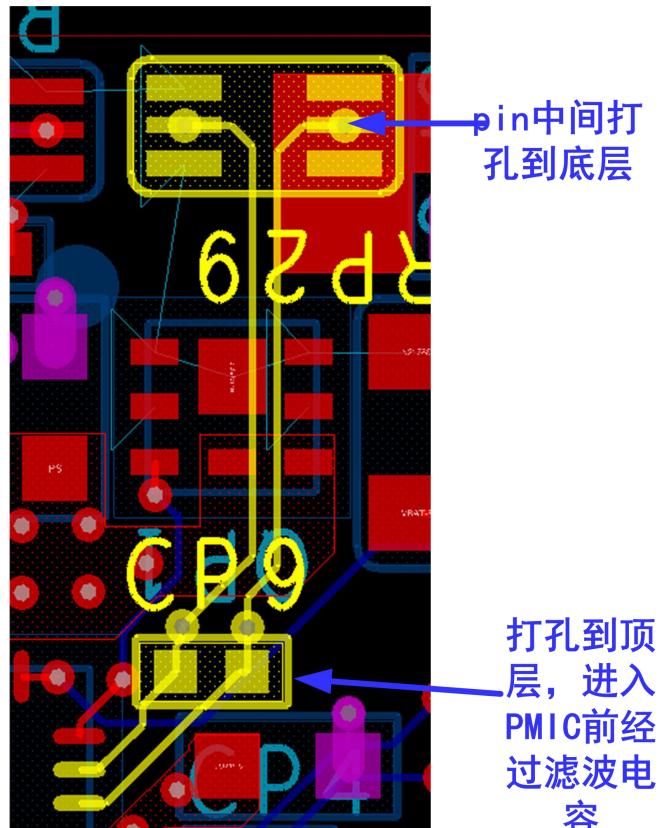

16. 电流采样路径用4~8mil即可，从电阻采样pin中间取点打孔到底层，差分走线到PMIC附近，如果电流采样有滤波电容，打孔到顶层进入PMIC前，先经过滤波电容。如下封装形式如下图所示：

# 19 PMU

17. 输入电容尽量靠近PMIC的LDOIN Pin，保证输入路径的宽度满足电流要求，通常100mA~1A；

18. 输出电容尽量靠近PMIC的LDOOUT Pin, 保证PMIC的输出经过LDO电容后再向负载供电，线径满足电流要求，通常为100mA~2A；

19. VREF的电容尽量靠近Pin脚，电容接地点尽量远离跳变点，避免干扰

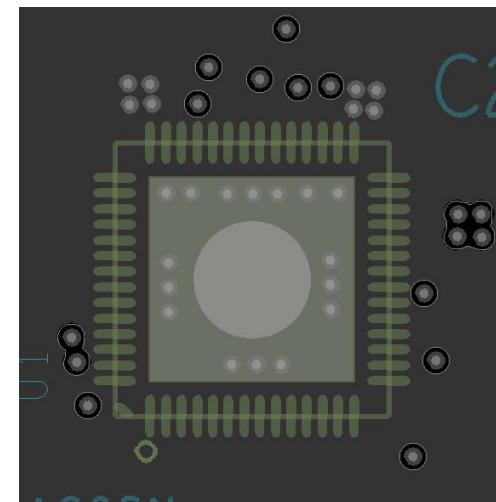

20. PMIC底部PAD多打孔到地层相连，在地层用全连接方式。如下图：

# 19 PMU

21. 系统与PMIC的通讯信号，也是跳变信号，避开敏感信号，采用4mil的走线。

22. PMIC辅助功能信号，如Led，TS等。没有过多要求。

23. PMIC有一些I/O口，具有LDO功能，或者Switch功能；走线时，注意线宽，尽量采用铺铜。

# 20 DRAM

1. SOC支持DDR3/3L、LPDDR2、LPDDR3，使用时需先确定DRAM的类型，以及单片的位宽，参考标案原理图连接

2. 主控和DRAM端每一个ZQ PIN都必须接240R-1%精度的下拉到地电阻.

3. SDQ0-SDQ7，SDQ8-SDQ15，SDQ16-SDQ23，SDQ24-SDQ31分别为4组数据线，若用DDR3/3L，则可以进行组内或者组间交换，若进行组间交换，则相应的SDQM和SDQS差分对也必须对应交换.

- 4.若用LPDDR2或者LPDDR3，则SDQ0-SDQ7，SDQM0，SDQ0，SDQS0B必须与主控一一对应连接，而其他高位的3组DQ以及高位的DQM和DQS差分对，则与DDR3类似，可视PCB走线难度程度进行组内或组间交换。

# 21 KEY

1. 键数选择，根据需要，直接去掉后面的按键。

2. 按键采用线控按键，KEYADC网络的采样范围为0-2V，在添加按键时保证按键按下后KEYADC网络电压范围为0-1.35V，并保证任意两个按键按下时KEYADC电压差必须 $\geq 0.15V$ 。

3. 如果不需要按键，若考虑SDK兼容，则KEYADC必须加100K上拉电阻到AVCC，否则KEYADC可以floating。

# 22 STACK UP

1. 四层板，叠层结构和阻抗控制建议如下（如果需调整板厚，请调整2、3层之间介质厚度，保持其他介质厚度不变）

| Total layers:                |                  | 4                        |               |                               |                       |                 |                   |

|------------------------------|------------------|--------------------------|---------------|-------------------------------|-----------------------|-----------------|-------------------|

| Board thickness:             |                  | 1.6 mm +/- 10%           |               |                               |                       |                 |                   |

| PCB material:                |                  | Typical FR4              |               |                               |                       |                 |                   |

| Surface finish:              |                  | ENIG(化学镍金)               |               |                               |                       |                 |                   |

| <b>Stackup Control Table</b> |                  |                          |               |                               |                       |                 |                   |

| ---                          |                  | <i>Stackup Structure</i> |               | <i>Impedance Requirements</i> |                       |                 |                   |

| Layer                        | Type             | Thickness (mil)          |               | Dk(with Sim Z0)               | Impedance spec (Ohms) | Reference layer | Width/space (mil) |

|                              | solder mask      | 0.5                      | SM            | 4.25                          |                       |                 | Sim Z0(Ohms)      |

| 1                            | TOP              | 1.6                      | 0.3oz+plating | 4.25                          | 50 +/- 10%            | 2               | 4                 |

|                              |                  |                          |               |                               | 90 +/- 10%            | 2               | 4.5/7.5           |

|                              |                  |                          |               |                               | 100 +/- 10%           | 2               | 3.8/8.7           |

| 2                            | prepreg          | 2.9                      | 1.0oz         | 4                             |                       |                 |                   |

|                              |                  |                          |               |                               |                       |                 |                   |

|                              |                  |                          |               |                               |                       |                 |                   |

| 3                            | GND              | 1.2                      | 1.0oz         | 4.5                           |                       |                 |                   |

|                              |                  |                          |               |                               |                       |                 |                   |

|                              |                  |                          |               |                               |                       |                 |                   |

| 4                            | core             | 50.0                     | 1.0oz         | 4                             |                       |                 |                   |

|                              |                  |                          |               |                               |                       |                 |                   |

|                              |                  |                          |               |                               |                       |                 |                   |

| 4                            | VCC              | 1.2                      | 1.0oz         | 4                             |                       |                 |                   |

|                              |                  |                          |               |                               |                       |                 |                   |

|                              |                  |                          |               |                               |                       |                 |                   |

| 4                            | BOTTOM           | 1.6                      | 0.3oz+plating | 4.25                          | 50 +/- 10%            | 3               | 4                 |

|                              |                  |                          |               |                               | 90 +/- 10%            | 3               | 4.5/7.5           |

|                              |                  |                          |               |                               | 100 +/- 10%           | 3               | 3.8/8.7           |

|                              | solder mask      | 0.5                      | SM            |                               |                       |                 |                   |

|                              | Board thickness: | 62.4                     |               |                               |                       |                 |                   |

# 22 STACK UP

2. 六层板，叠层结构和阻抗控制建议如下（如果需调整板厚，请调整3、4层之间介质厚度，保持其他介质厚度不变）

|                  |                |

|------------------|----------------|

| Total layers:    | 6              |

| Board thickness: | 1.6 mm +/- 10% |

| PCB material:    | Typical FR4    |

| Surface finish:  | ENIG(化学镍金)     |

Stackup Control Table

| --- | Stackup Structure |                  | Dk(with Sim Z0) | Impedance Requirements |                 |              |         |       |  |

|-----|-------------------|------------------|-----------------|------------------------|-----------------|--------------|---------|-------|--|

|     | Layer             | Type             | Thickness (mil) | Impedance spec (Ohms)  | Reference layer | Sim Z0(Ohms) |         |       |  |

| 1   | TOP               | soldermask       | 0.5             | 4.25                   | 50±10%          | 2            | 4       | 52.18 |  |

|     |                   |                  |                 |                        | 90±10%          | 2            | 4.5/7.5 | 90.03 |  |

|     |                   |                  |                 |                        | 100±10%         | 2            | 3.8/8.7 | 98.5  |  |

| 2   |                   | prepreg          | 2.9             | 4                      |                 |              |         |       |  |

|     |                   | GND1             | 1.2             |                        |                 |              |         |       |  |

|     |                   | core             | 4.0             |                        |                 |              |         |       |  |

| 3   | SIG               |                  |                 | 4.2                    | 50±10%          | 2&4          | 4       | 51.67 |  |

|     |                   |                  |                 |                        | 90±10%          | 2&4          | 4.5/7.5 | 88.18 |  |

|     |                   |                  |                 |                        | 100±10%         | 2&4          | 3.8/8.7 | 96.3  |  |

| 4   |                   | prepreg          | 40.0            | 4.5                    |                 |              |         |       |  |

|     |                   | GND2             | 1.2             |                        |                 |              |         |       |  |

|     |                   | core             | 4.0             |                        |                 |              |         |       |  |

| 5   |                   | VCC              | 1.2             | 4.2                    |                 |              |         |       |  |

|     |                   |                  |                 |                        |                 |              |         |       |  |

|     |                   | prepreg          | 2.9             |                        |                 |              |         |       |  |

| 6   | BOTTOM            |                  |                 | 4                      | 50±10%          | 5            | 4       | 52.18 |  |

|     |                   |                  |                 |                        | 90±10%          | 5            | 4.5/7.5 | 90.03 |  |

|     |                   |                  |                 |                        | 100±10%         | 5            | 3.8/8.7 | 98.5  |  |

|     |                   | soldermask       | 0.5             | SM                     |                 | 4.25         |         |       |  |

|     |                   | Board thickness: | 62.8            |                        |                 |              |         |       |  |

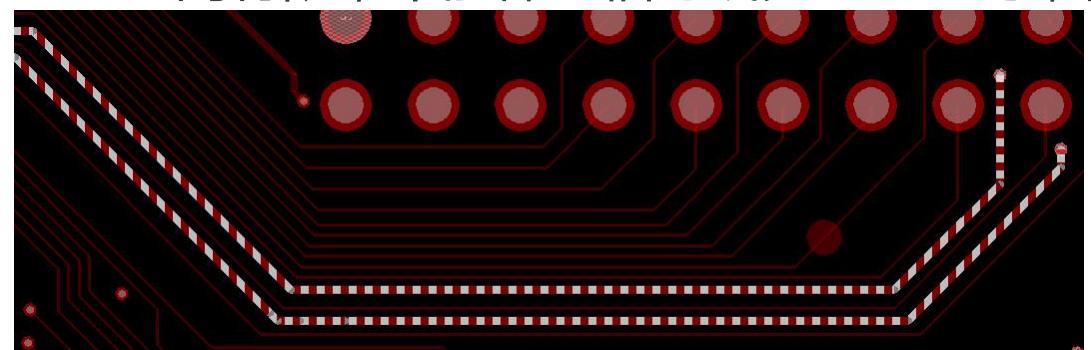

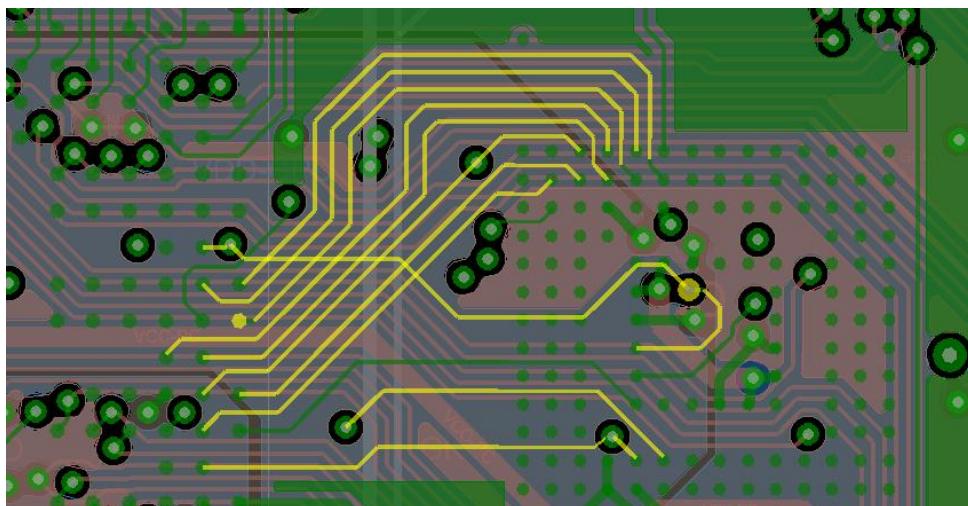

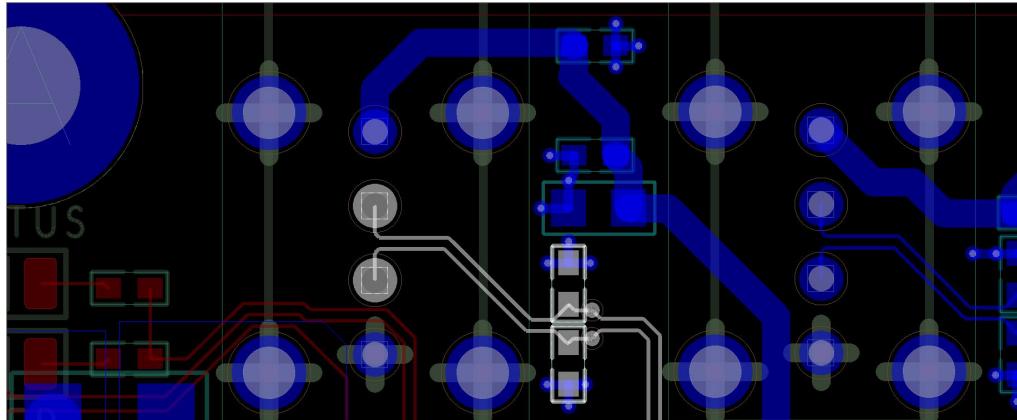

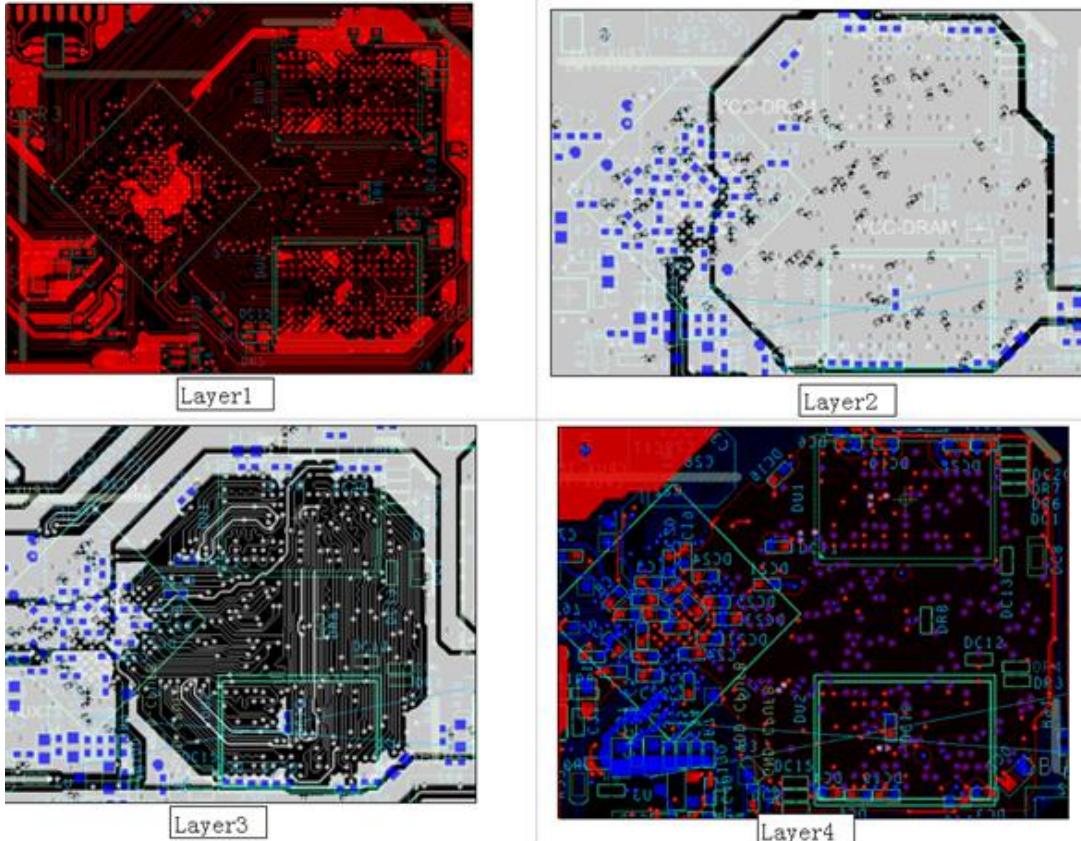

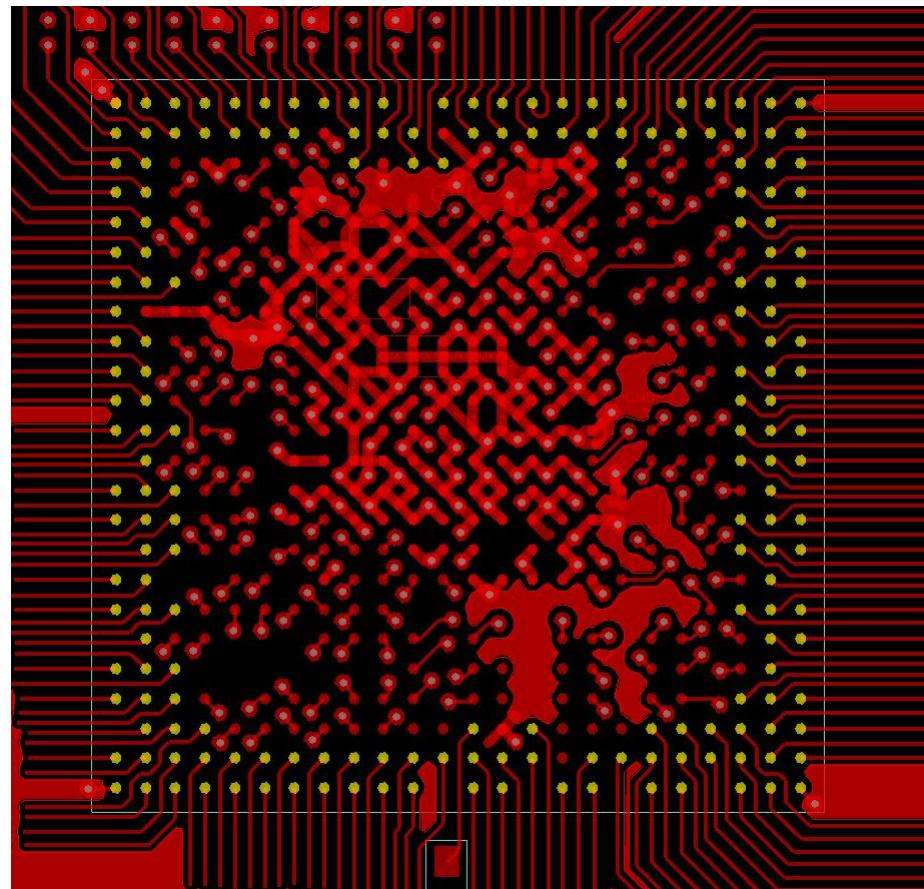

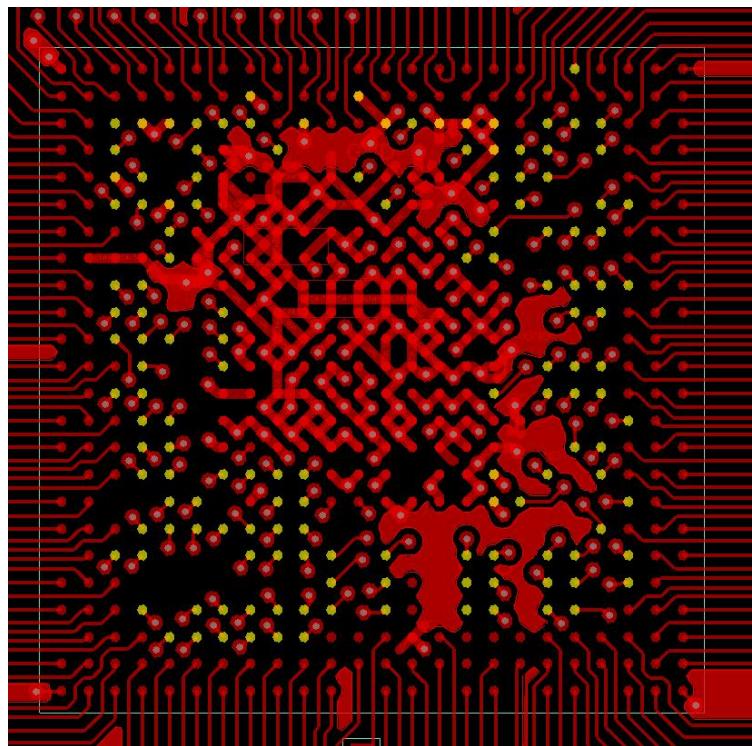

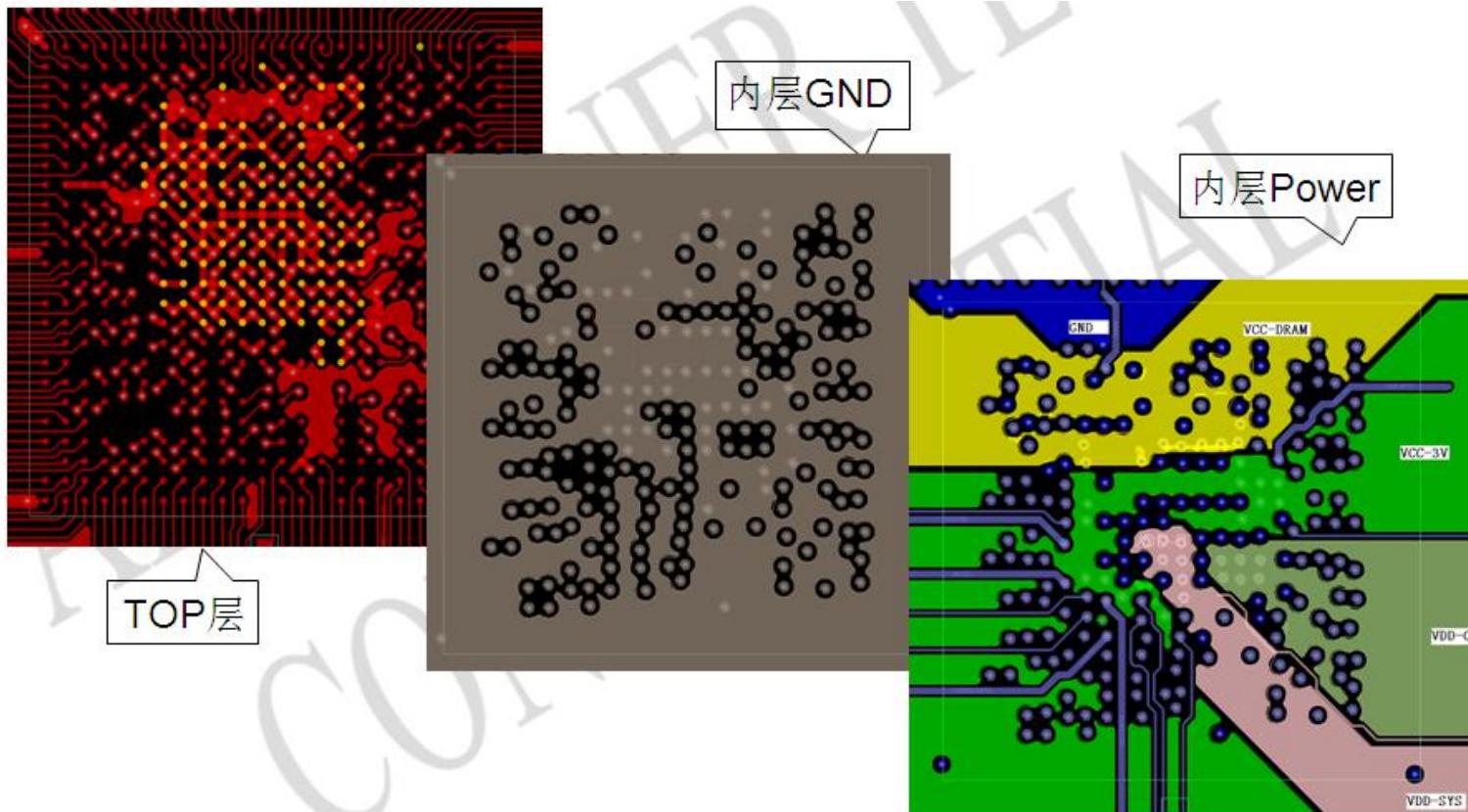

# 23 SOC FANOUT

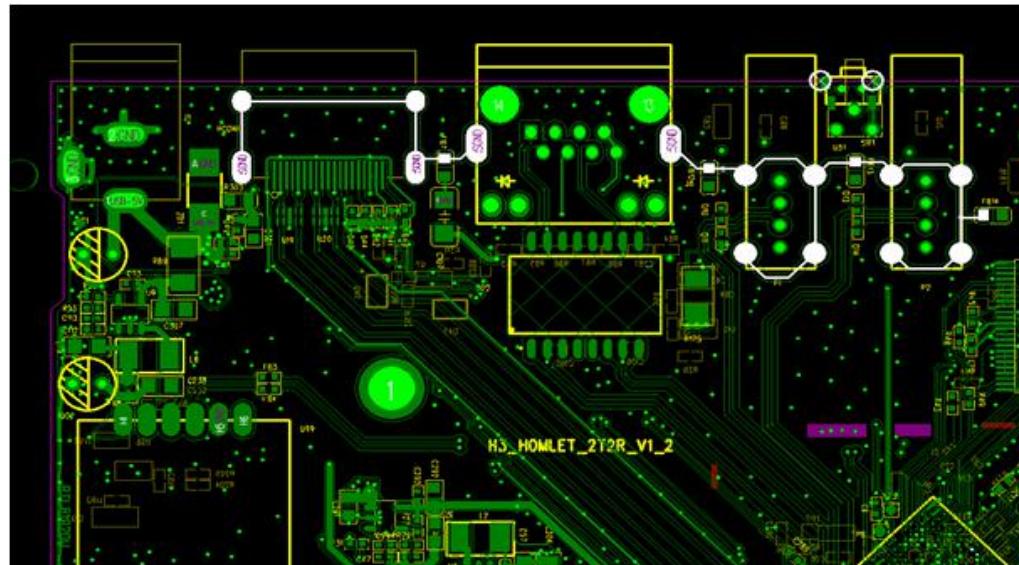

1. 第一圈、第二圈、第三圈部分Ball，可以从顶层直接拉出走线（线宽4 mil，线距4 mil）

# 23 SOC FANOUT

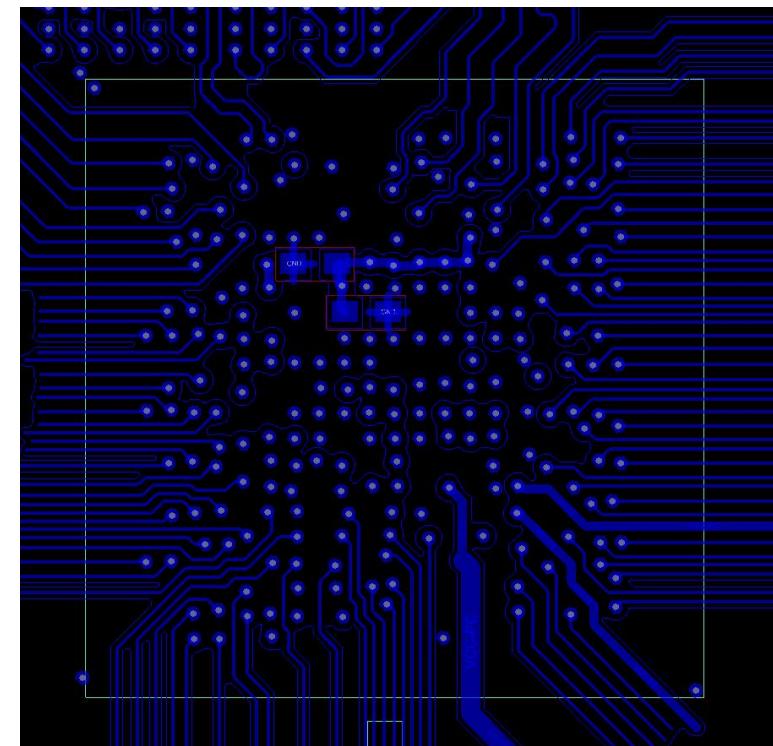

2. 第四到五圈的Ball，用8/16mil过孔扇出，从Bottom层出线 ( 6层板也可从内层信号层出线 )

TOP层

BOTTOM层

# 23 SOC FANOUT

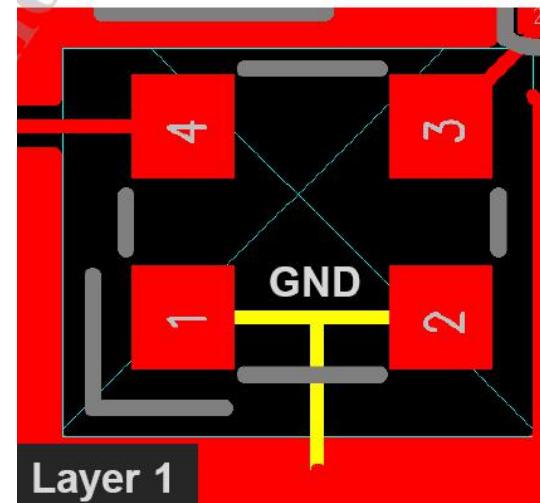

3. 中间Power和GND的球，用8/16mil过孔从内层覆铜出线，注意留出尽量多的覆铜通道：

# 24 REVISION HISTORY

V0.1

20180626

初稿

# THANKS